The Silicon Creations wide-range 0.6Gbps to 4.0Gbps 4-lane Deserializer and Serializer macros include all high-speed analog functions for four lanes of high-speed data transport between chips over FR4 and similar PCBs and over high quality cables. Trimmable on-die termination and linear equalization are included to compensate for channel loss enabling longer cables. They are optimized for low power operation and is suitable for a variety of chip-chip communication protocols.

Low Power Multiprotocol SerDes PMA

Overview

Key Features

- Very wide CDR range { operates with data rates from 0.6Gbps to 4.0Gbps

- Compatible with JESD204A, JESD204B, OIF-CEI-6G-SR, CPRI, SGMII, eDP and V-by-One 1.5

- Four lanes sharing bias to save area and power may be placed any number of times

- Switchable receiver equalization to improve signal integrity and compensate for lossy channels

- Trimmable on die termination for excellent signal integrity

- High-speed loop-back path simplifes production testing when used together with serial data sources

- Comprehensive power-down control to optimize power modes

- Small die area [only 0.14mm2/lane] including pads

- 1.8V I/O voltage operation

- Auxiliary output dividers (1/30,1/40,1/50) for compatibility with multiple PCS designs

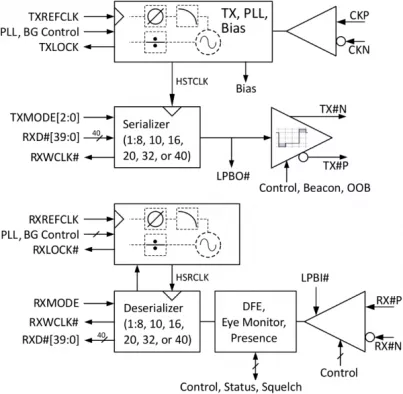

Block Diagram

Applications

- UHD-TV (4k TV) displays

- MFPs

- Scanners

- Semi-custom chip-chip interfaces

- Low power backplanes

Deliverables

- GDSII

- CDL Netlist (MG Calibre Compatible)

- Functional Verilog Model

- Liberty timing models (.lib)

- LEF

- Application Note with integration and production test guidelines

Technical Specifications

Foundry, Node

TSMC 28 HPC+, GF 28 SLP

Maturity

Production

Availability

Available Now

GLOBALFOUNDRIES

In Production:

28nm

SLP

Silicon Proven: 28nm SLP

Silicon Proven: 28nm SLP

TSMC

In Production:

28nm

HPCP

Pre-Silicon: 28nm HPC

Pre-Silicon: 28nm HPC

UMC

Silicon Proven:

28nm

HLP