Includes all high-speed analog functions for serializer and deserializer PMA. Optimized for low power operation.

Proven compatibility -- In mass production with common V-by-One parts.

Low Power V-by-One HS SerDes

Overview

Key Features

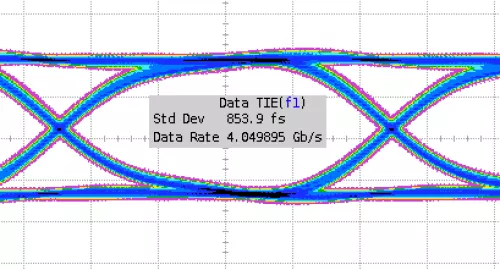

- Data rates of <600Mb/s to 4Gb/s

- Compatible with FibreChannel, JESD 204, V-by-One, CPRI, OIF-CEI-6G-SR

- Separate PLLs for Tx and Rx support a single crystal reference clock or separate references from 20MHz to 400MHz

- Separate Serializer and Deserializer macros simplify assembly of multiple configurations

- IO library integrated to simplify integration and lower ESD risk

- Trimmable on-die termination ensures excellent signal integrity

- Comprehensive power-down control

Block Diagram

Applications

- UHD-TV (4k TV) displays

- MFPs

- Scanners

- Semi-custom chip-chip interfaces

- Low power backplanes

Deliverables

- GDSII

- CDL Netlist (MG Calibre Compatible)

- Functional Verilog Model

- Liberty timing models (.lib)

- LEF

- Application Note with integration and production test guidelines

Technical Specifications

Foundry, Node

TSMC 40nm; UMC28nm

Maturity

Mass Production

Availability

Available Now

TSMC

In Production:

40nm

LP

UMC

Pre-Silicon:

28nm

HLP