The wide-range 125Mbps to 16Gbps 2-lane SerDes macro includes all high-speed analog/mixed-signal functions including PCS, Loopback, DFT and Calibration for two lanes of high-speed data transport between chips over FR4 and similar PCBs/backplanes and over quality cables. Macro is optimized for low power operation and is suitable for a variety of communication protocols. Trimmable on-die termination, linear equalization (CTLE) and Decision Feedback Equalizer are included to compensate for channel loss enabling longer cables. An Eye Monitor is included to verify the eye opening at the data slicer.

125Mbps to 16Gbps Multi-protocol SerDes PMA

Overview

Key Features

- Very wide CDR range -- operates with data rates from 0.125Gbps to 16Gbps

- Extremely low jitter suitable for Enterprise SerDes applications

- Compatible with USB 3.x SuperSpeed Bus Gen 2, OIF-CEI-6G/11G-SR/MR/LR, JESD204A/B/C, CPRI1-9, PCIe1/2/3/4, OTN (OTU1/2), SMPTE SDI, 10G-KR, XAUI, SG- MII, V-by-One, (e)DP (RBR/HBR/HBR2/3)

- Two lanes sharing bias to save area and power may be placed any number of times

- Programmable receiver equalization and 5-tap DFE to improve signal integrity and compensate for lossy channels

- Flexible line driver with highly programmable levels and 3-tap FFE for pre- and post-emphasis

- Fast CDR capable of burst mode and comfortably meeting DisplayPort JTOL

- Low-latency version available with <13UI round-trip PMA latency

- Trimmable on-die termination for excellent signal integrity

- Comprehensive power-down control to optimize power modes

- Flip-chip packaging

Benefits

- Shares same core design as the PMA in the Microchip PolarFire FPGA - low power, low area and excellent performance

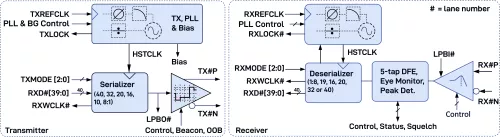

Block Diagram

Applications

- Programmable devices needing to support over 30 different protocols

- AFE-FPGA interfaces

- Solid-state storage devices

- 10G-KR Ethernet

- SATA interfaces

- UHD-TV (8k TV) displays

- PC graphics cards / monitors, mobile devices, notebooks (DisplayPort)

- MFPs

- SFF-8431

- XFI

- 1000BASE-SX or LX

- ONU PON

- Scanners

- Semi-custom chip-chip interfaces

- Backplanes

- SGMII for Automotive

Deliverables

- GDSII

- CDL Netlist

- Functional Verilog Model (.v)

- Liberty timing model (.lib)

- LEF

- Application Note with integration and production test guidelines

- Signal integrity simulations using customer package models

Technical Specifications

Foundry, Node

TSMC 4nm, 5nm, 6nm, 7nm, 12nm, 16nm, 28nm, 40nm; GlobalFoundries 12nm, 40nm; UMC 28nm

Maturity

Mass Production

Availability

Now

GLOBALFOUNDRIES

Pre-Silicon:

12nm

Silicon Proven: 40nm LP

Silicon Proven: 40nm LP

TSMC

In Production:

12nm

Pre-Silicon: 28nm HPCP , 40nm G

Silicon Proven: 16nm , 40nm G , 40nm LP

Pre-Silicon: 28nm HPCP , 40nm G

Silicon Proven: 16nm , 40nm G , 40nm LP

UMC

In Production:

28nm

HLP