OPENEDGES, the memory system IP provider, including DDR memory controller, DDR PHY, on-chip interconnect, and NPU IP together as an integrated solution or independent IP. They are tightly combined to bring synergy for high performance and low latency. OPENEDGES' integrated IP solutions are market and silicon-proven, featuring advanced architectures and proprietary technologies that enable customers to shorten their design and verification processes.

OMC – HBM3 Memory Controller is a small & highly configurable IP. It provides high performance through advanced memory controller design based on a proprietary out-of-order scheduling algorithm and high-speed implementation technique. Demand for more DRAM bandwidth is getting stronger than ever in a quest to improve user experiences (e.g., higher image resolution). Given the limited amount of physically available DRAM bandwidth, highly efficient memory controller IP is becoming a very critical issue everywhere. With our OMC – HBM3 Memory Controller, SoCs can save significant amounts of area & power consumption and meet next-generation SoC’s DRAM bandwidth requirements.

High Performance HBM, HBM3 Memory Controller

Overview

Key Features

- Compliant with JEDEC standard for HBM3

- DRAM SID of up to 4

- Channel mode: x32 for each Pseudo Channel

- Support DBIac

- Support Command/Address Parity, Data Parity

- Support for dynamic DRAM frequency scaling

- Address region-based security control support

- Automated low-power control of DRAM devices

- Flexible refresh control

- DFI 5.0 Interface Compliant

- Priority per request based on AXI QoS signal

- A proprietary out-of-order scheduling algorithm

- Ultra-low power consumption with HW-controlled dynamic DRAM frequency scaling

- Automatically handles training activities required for frequency change

- Muti-port master interface (optional)

Benefits

- Intensive utilization using a proprietary out-of-order scheduling algorithm

- Extremely low latency using a latency-aware algorithm. Safety & Security

- Reliability using ECC and Security Firewall

- Highly PPA based on a proprietary architecture

- Active QoS control combined with ORBIT™ interconnect (OIC) for maximum performance & flexibility.

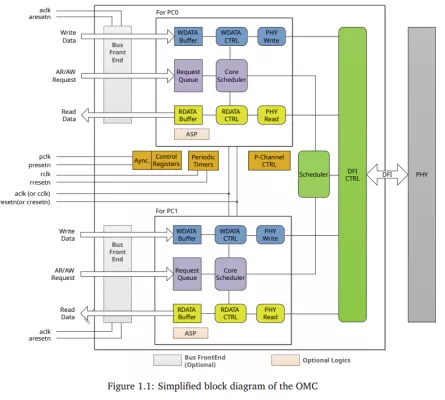

Block Diagram

Applications

- Automotive

- Application Processors

- Digital Baseband Modems

- Set-Top-Box

- Digital TV

- OTT

- Surveillance

- IoT, Enterprise

- SSD Controllers

Deliverables

- OMC is packaged with the following items to all eligible companies:

- IP core RTL

- Standalone Simulation Environment

- Management SW

- IP Documentation

Technical Specifications

Availability

Now

Related IPs

- DDR4 Controller - Validates memory compliance, optimizes performance, ensures reliability

- GDDR5 Controller - Verifies memory compliance, boosts performance, and ensures reliability

- LPDDR5 Controller - Validates memory controllers for high-speed, power-efficient performance

- HBM3E/3 Memory Controller

- HBM4 Memory Controller

- HBM3 Memory Model