The eUSB2V2 Verification IP provides an effective & efficient way to verify the components Supporting eUSB2V2 Revision 1.0 Specification The eUSB2V2 VIP is fully compliant with standard eUSB2V2 specifications from USB-IF. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design cycle time.

eUSB2 v2 Verification IP

Overview

Key Features

- Supports eUSB2-v2 extended Symmetric data rates (HSSx), extended Asymmetric data rates (HSUx & HSDx)

- Supports Scrambling and Bit Stuffing

- Supports the Disconnect/Connect with Analog Ping in Extended High-Speed Signaling at nave mode.

- Supports Protocol Extended Token transactions for LPM Ack handshake.

- Supports all eUSB2-v2 Repeater architecture and operations Host Reset, Low power states, Resume, Remote Wakeup, Disconnect Signaling between Host and Peripheral device.

- Compliant with eUSB2-v2 specification rev 1.0.

- eUSB2-v2 PHY and eUSB2-v2 is fully compliant to the USB2.0 Rev 2.0 Specificaon that supports high-speed operation.

- Supports any eUSB2-v2 device in nave mode.

- Supports UTMI/UTMI+ Parallel Mode.

- Supports link power management LPM-L1 (L1) and Suspend (L2).

- Supports register access protocol (RAP) for eUSB2-v2 devices or repeater configurations.

- Fully compliant to USB2.0 base spec at the protocol layer.

- Fully compliant to the USB2.0, xHCI 1.1, Utmi+ 1.0 Transceiver Interface Specificaon with backward compality to USB 1.1.

- Supporting On-The-Go which is fully compliant OTG Rev 2.0, V1.1a.

- Supports xHCI functionality on Host model.

- Host Model Supports up to 127 devices of any tier level.

- Supports 15 IN and 15 OUT and 1 control endpoint for each device.

- User-controlled device aach/ detach function.

- Supports Extended High Speed (HSx) Functionality.

- Supports all USB2 transfer types; Control, Bulk, Interrupt, and Isochronous.

- Supports High Bandwidth ISO and Interrupt transfers.

- Supports resume and remote wake-up.

- Configurable Utmi+ Interface width 8 and 16 bits.

- Supports randomisation for packet fields and data payload with or without error injection.

- Comprehensive Compliance Test Suite for verification.

- Supports all types of error injection (control transfer error injection (Request error), PID, CRC, Interpacket Delay, Sync, EOP, Bitstuff etc.) and detection.

- Supports detailed activity log files for individual layers for Debugging.

- Supports dynamically configurable modes.

- Strong Protocol Monitor with real-time exhaustive programmable checks.

- Supports configuring Protocol Timers and intentional error masking.

- On the fly protocol checking using protocol check functions, and assertion checks for UTMI Interface.

- Built in Coverage analysis.

- Provides a comprehensive user API (callbacks) in Host and Device.

Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- 24x5 customer support & response under 90 Min.

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity examples for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

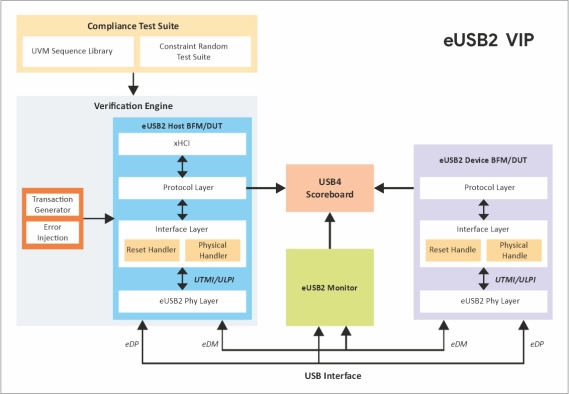

Block Diagram

Deliverables

- eUSB2V2 HOST/DEVICE/REPEATER BFMs

- eUSB2V2 Bus Monitor, Protocol Monitor and Scoreboard.

- BFM Agents for:

- Protocol Layer

- PHY Layer

- Compliance Test Suite (CTS)

- Stress test for each standard layer

- xHCI VIP compatible with Revision 1.0

- Integration Guide, User Manual and Release Notes

- GUI analyser to view simulation packet flow