The AMBA AXI STREAM Verification IP provides an effective & efficient way to verify the components interfacing with the AMBA® AXI5 stream and AXI4 stream bus of an IP or SoC. The AMBA AXI5 stream and AXI4 stream VIP are fully compliant with standard AMBA® AXI5 stream and AXI4 stream specifications from ARM. This VIP is a lightweight VIP with an easy plug-and-play interface so that there is no hit on the design cycle time.

AMBA AXI STREAM Verification IP

Overview

Key Features

- Compliant with AMBA® AXI5- Stream and AXI4-Stream.

- Support for all types of AMBA AXI5-Stream and AXI4-STREAM components.

- Supports parameterized data widths.

- Supports byte stream transmission number of data and null bytes.

- Supports a wide variety of different stream types such as single transfer, Packet-group of bytes, Frame-The highest level of byte grouping in an AXI5 and AXI4 stream.

- Supports Continuous aligned, unaligned, and Sparse streams.

- Supports all Byte types i.e. Data byte, position byte, and Null byte.

- Supports Data Merging, packing, and width conversion.

- Supports two-byte qualifiers indicators TKEEP and TSTRB.

- Supports wake-up signaling and user signaling property using TUSER.

- Supports source and destination signaling TID and TDEST.

- Supports continuous packet stream transmission.

- Supports Interleaving transfers from different streams on a transfer-by-transfer basis

- Supports Transfer ordering feature this makes AXI-Stream protocol all transfers remain ordered.

- Supports parity check signals for byte parity interface protection

- Wide range of strict programmable protocol checks, and config checks.

- Bus assertion for all protocol scenarios.

- Bus & configuration coverage, assertion coverage.

- Multiple constraints to generate various protocol scenarios & corner cases.

- Supports a wide variety of static and dynamic error injection scenarios.

- Callbacks for Master, Slave, Monitor, and Scoreboard.

- Components can be re-configured on the fly for each new packet.

- Configurable bus, id, and user signaling width.

- All transactions configurable with user define values (for e.g. tid, tdest, tdata, tstrb, tkeep).

- A number of Interleaving streams can be configured to any number as required.

- Each and every bus activity can be seen in TruEye, Use for easy debugging and analysis.

- Automated Error/warning reporting, Severity control, suppression & detailed description.

- VIP can be plugged in with any type of DUT which supports AXI5/4 stream specifications.

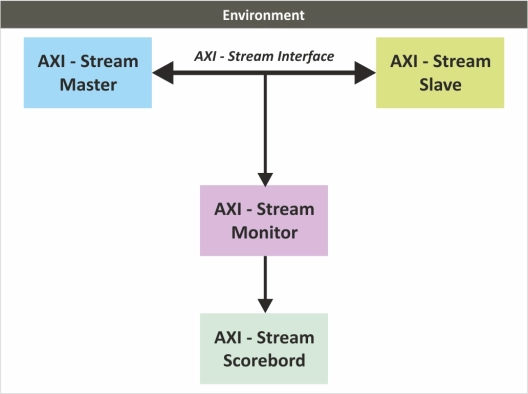

Block Diagram

Technical Specifications

Related IPs

- Enhanced SPI Controller IP- Master/Slave, Parameterized FIFO, AMBA APB / AHB / AXI Bus. Supports eSPI Master & Slave and SPI Master & Slave functions

- SPI Slave IP transfers to/from a AMBA APB, AXI, or AHB Interconnect

- AMBA AXI STREAM Verification IP

- AXI Verification IP

- AHB Lite Verification IP

- Low Pin Count (LPC) controller verification IP