Noc Interconnect IP

Filter

Compare

15

IP

from

8

vendors

(1

-

10)

-

Network-on-Chip (NoC) Interconnect IP

- AMBA AXI / APB / AHB protocol compliant

- Configurable number of masters and slaves

-

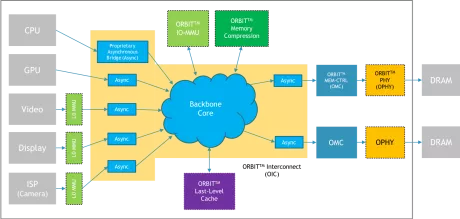

High speed NoC (Network On-Chip) Interconnect IP

- The ORBIT On-Chip Interconnect (OIC) delivers exceptional performance, and SoC design flexibility based on automated end-to-end interconnect generation flow.

- It enables high-speed routing with pre-calculated routing path details and supports higher speed, low latency, and floorplan flexibility.

-

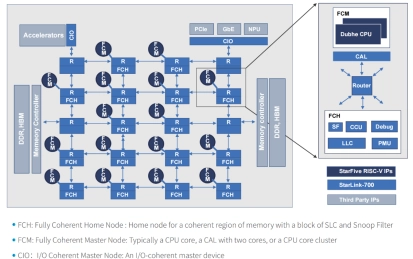

High-scalable, high-performance Interconnect fabric IP with cache coherence support

- High bandwidth, low power consumption, low latency

- Support Component Aggregation Layer (CAL)

- Topology: Mesh

- Support multiple I/O Coherent Master Nodes (CIO)

- Maximum node count: 12x12

-

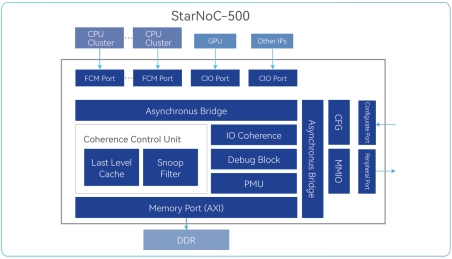

Interconnect fabric IP with cache coherence support

- StarNoC-500 is the vendor's first self-developed interconnect fabric IP with cache coherence support, supporting the construction of multi-cores and SoC.

-

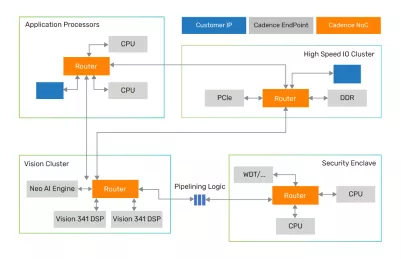

NoC System IP

- Packetization allows a reduction of the wire count

- Significant reduction of the complexity of large crossbars by partitioning them into smaller ones

- Introduction of pipelining to links with heavy loads, allowing the NoC to operate faster

-

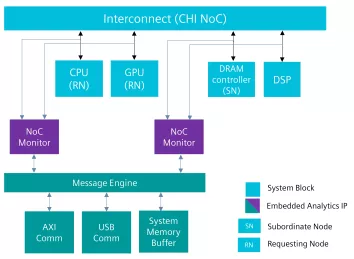

Tessent NoC Monitor

- Full transaction and trace-level visibility of traffic

- Wide range of measurements, analytics statistics: transactions, bus cycles, latency, duration, beats, concurrency

-

Coherent Network-on-Chip (NOC)

- Node Protocols: ACE4, ACE5 and CHI

- Architected to significantly reduce routing congestion for many-core systems

- Integrated with SkyeChip’s Home Agent and swappable with any other proprietary coherency handlers

- Supports operating frequencies up to 2GHz with assists in high frequency timing closures

-

Non-Coherent Network-on-Chip (NOC)

- Node Protocols: AXI4, AXI5, AXI-Stream, APB and proprietary protocols

- Architected to reduce routing congestion and to ease high frequency timing closure

- Supports operating frequencies up to 2GHz

- Supports source synchronous and synchronous clocking topologies

-

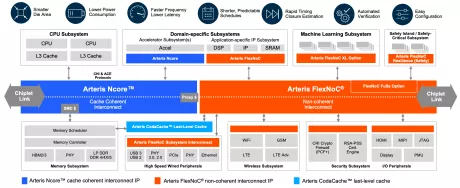

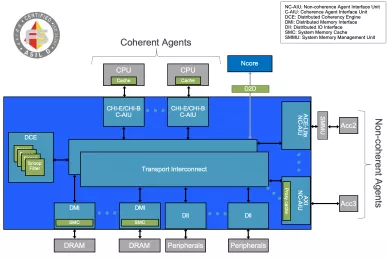

Ncore 3 Coherent Network-on-Chip (NoC)

- Supports multiple coherent agents, including Armv9 and RISC-V CPU clusters

- AMBA CHI-E, CHI-B and ACE interoperability, as well as ACE-Lite and AXI

- Low-latency proxy caches for efficient and quick integration of hardware accelerators into the coherent domain

- Configurable last-level caches

-