NVM Express IP

Welcome to the ultimate NVM Express IP hub! Explore our vast directory of NVM Express IP cores.

NVMe IP cores are compliant with NVM Express base specificationthat performs memory transfer to or from the NVMe storage like SSDs. These IP cores are designed to handle NVMe protocols without the need for external DDR memory via a PCIe interface. NVMe IP cores are ideal for applications that require large storage capacity with high performance and are available with flexible vendor-specific PCIe IP to access SSD.

All offers in

NVM Express IP

Filter

Compare

30

NVM Express IP

from 14 vendors

(1

-

10)

-

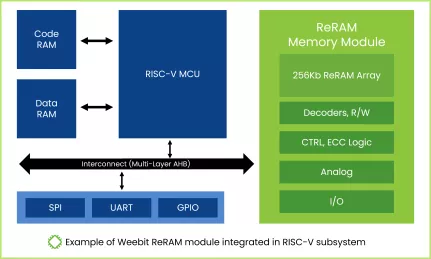

ReRAM NVM in SkyWater 130nm CMOS

- Technology: 130nm, SkyWater S130

- Mask Adder: 2

- Supply Voltage: 1.8V Read, 1.8V+3.3/3.6V Program

- Read Access Time: <20nsec

- Operation Temp.: -40°C - 125°C (can be extended to -55°C)

- Capacity: 256 Kbit (can be customized for 128Kbit - 2Mbit)

- Data Bus Width (Read): 32-bit (can be customized to 16-bit to 128-bit)

-

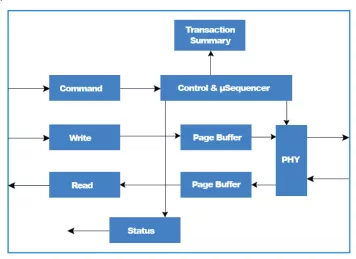

ONFI Flash Controller

- AXI System Interface

- NAND Flash

-

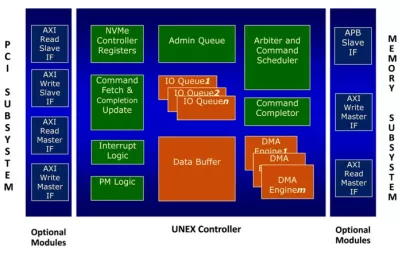

Universal NVM Express Controller (UNEX)

- Compliant to NVM Express 1.1

- Support for configurable number of IO Queues

- Support for configurable Queue depth

-

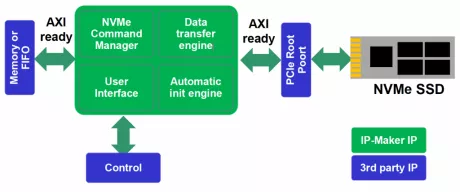

High Performance Embedded Host NVMe IP Core

- Automatic init engine: PCIe and NVMe device initialization, hardware discovering

- User Interface: memory configuration and input for the transfer request by the API

- NVMe command manager: translation of the data request from API into a NVMe command. Submission and completion pointers management

- Data Transfer Engine: management of the data transfer between the NVMe SSD and the FIFO/memory

-

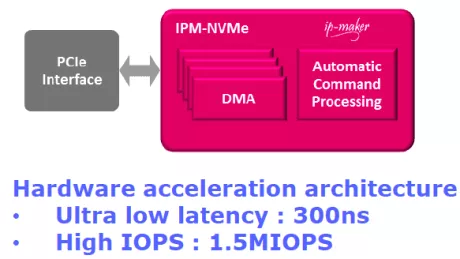

High Performance NVMe for PCIe-based storage

- NVM Express Compliant

- Automatic Command Processing

- Multi-Channel DMA

- Up to 65536 I/O queues

- Weighted round robin queue arbitration support

- All commands/log management

-

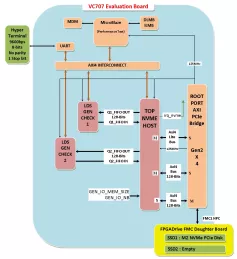

NVME-HOST-IP VIRTEX 7

- - PCIe RP and EP register configuration is done automatically.

- – NVMe register configuration is done automatically.

- – Able to manage 8 Name Spaces.

- – Able to manage until 16 IO Queue to fit specific user requirement. Each IO Queue is independent.

-

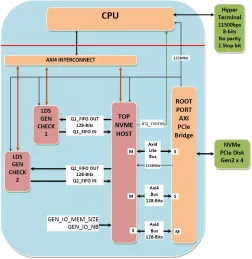

Xilinx Kintex 7 NVME HOST IP

- - PCIe RP and EP register configuration is done automatically.

- - NVMe register configuration is done automatically.

- - Able to manage 8 Name Spaces.

- - Able to manage until 16 IO Queue to fit specific user requirement.

-

Xilinx ZYNQ NVME HOST IP

- -PCIe RP and EP register configuration is done automatically.

- – NVMe register configuration is done automatically.

- – Able to manage 8 Name Spaces.

- – Able to manage until 16 IO Queue to fit specific user requirement. Each IO Queue is independent.

-

Xilinx UltraScale Plus NVME Hhost IP

- PCIe RP and EP register configuration is done automatically.

- NVMe register configuration is done automatically.

- Able to manage 8 Name Spaces.

-

Xilinx Ultra Scale NVME Host IP

- This IP can be customized according to specific needs (application-specific requirement).