HBM IP

HBM IP (High Bandwidth Memory Interface) cores enable high-speed data transfer between processors and memory, providing a significant performance boost for memory-intensive applications. Supporting advanced memory technologies like HBM1, HBM2, and HBM2E, HBM IP cores deliver ultra-fast data access, low latency, and high bandwidth, making them ideal for applications such as high-performance computing (HPC), artificial intelligence (AI), gaming, and data centers.

All offers in

HBM IP

Filter

Compare

63

HBM IP

from 12 vendors

(1

-

10)

-

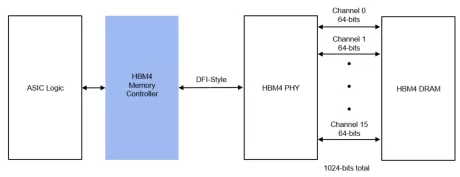

HBM4 Memory Controller

- Supports HBM4 memory devices

- Supports all standard HBM4 channel densities (up to 32 Gb)

- Supports up to 10 Gbps/pin

- Refresh Management (RFM) support

- Maximize memory bandwidth and minimizes latency via Look Ahead command processing

- Integrated Reorder functionality

-

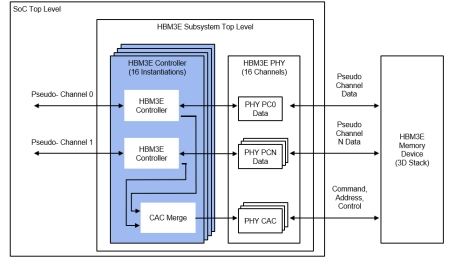

HBM3E/3 Memory Controller

- Supports HBM3E / HBM3 memory devices

- Supports all standard HBM3 channel densities (up to 32 Gb)

- Supports up to 9.6 Gbps/pin (HBM3E) or 8.4 Gbps/pin (HBM3)

- Refresh Management (RFM) support

- Maximizes memory bandwidth and minimizes latency via Look-Ahead command processing

- Integrated Reorder functionality

-

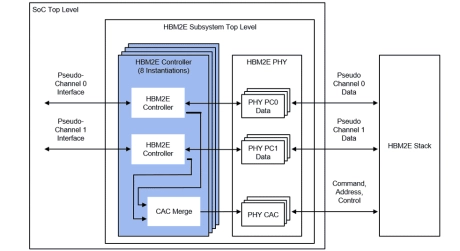

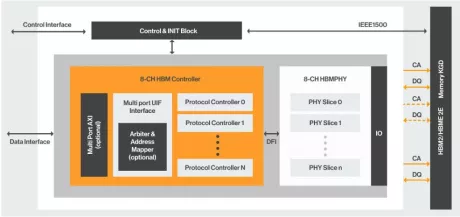

HBM2/2E Memory Controller Core

- Supports HBM2E and HBM2 devices

- Supports all standard HBM2/2E channel densities (4, 6, 8, 12, 16, 24 Gb)

- Supports data rates of up to 3.6 Gbps/pin

- Can handle two pseudo-channels with one controller or independently with two controllers

- Queue-based interface optimizes performance and throughput

- Maximizes memory bandwidth and minimizes latency via Look-Ahead command processing

-

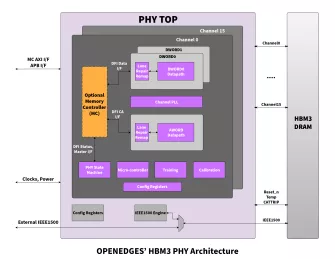

HBM3 PHY

- Offers superior power efficiency and supports up to 4 active operating states and dynamic voltage scaling. With a fully optimized hard macro design on advanced process technology,

- Delivers highly reliable industry-leading performance.

- Implements an optimized micro bump array and is delivered as hard macro GOS ready for integration into 2.5D system applications.

-

HBM3 Controller

- Ideal for applications involving graphics, high-performance computing, high-end networking, and communications that require very high memory bandwidth, lower latency, and more density.

-

High Performance HBM, HBM3 Memory Controller

- DRAM Supports

- High Performance

- Low Power Consumption

-

HBM3 PHY IP at 7nm

- Unbeatable performance-driven and low-power-driven PPA

- Ultra-low read/write latency with programmable PHY boundary timing

-

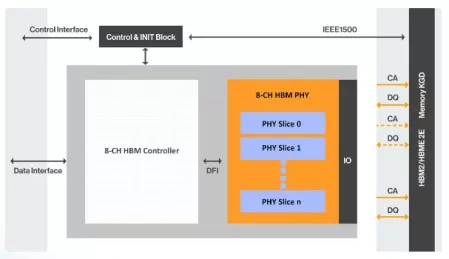

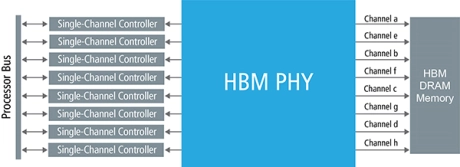

HBM2E/HBM2 PHY

- Advanced clocking architecture minimizes clock jitter

- DFI PHY Independent Mode for initialization and training

- IEEE 1500 interface, Memory BIST feature, and loop-back function

- Designed for optimized interposer routing

- Pin programmable support for lane repair

-

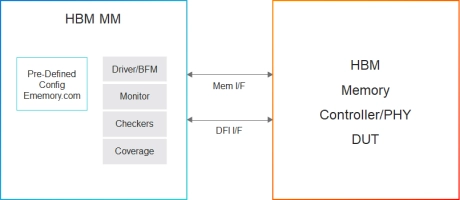

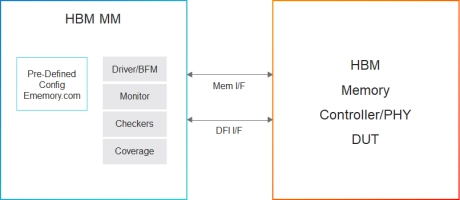

Simulation VIP for HBM3

- Speed (MHz)

- Clock: 1800MHz; data rate: 7.2Gbps/pin

- Mode Registers

- All 16 mode registers are supported

-

Simulation VIP for HBM

- Speed (MHz)

- 1800MHz (3.6 Gbps/pin)

- Device Density

- Supports a wide range of device densities from 1Gb to 24Gb