PCI Express Phy IP

Welcome to the ultimate PCI Express Phy IP hub! Explore our vast directory of PCI Express Phy IP

All offers in

PCI Express Phy IP

Filter

Compare

307

PCI Express Phy IP

from 24 vendors

(1

-

10)

-

1 to 64 Gbps PCI-Express (PCIe) 6.0 and CXL 3.0 PHY

- High speed performance

- Low power architecture

- Robust training

-

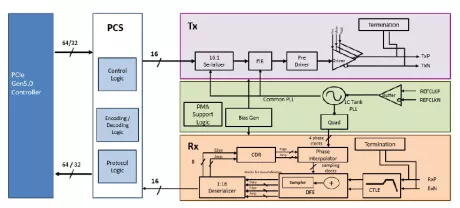

PCIe 5.0 PHY IP for Storage and High-Bandwidth Connection

- Fully compliant with PCI Express Base 5.0 electrical specifications

- Compliant with PIPE5.2 (PCIe) specification

- Supports all power-saving modes (P0, P0s, P1, and P2) defined in PIPE4.4.1 spec

-

PHY for PCIe 6.0 and CXL

- Architecture optimized for HPC, AI/ML, storage, and networking

- Ultra-long reach, low latency, and low power

- Advanced DSP delivers unmatched performance and reliability

- Comprehensive real-time diagnostic, monitor, and test features

- Bifurcation support for x1, x2, x4, x8, and x16 lanes

-

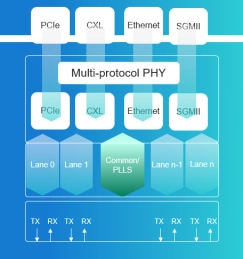

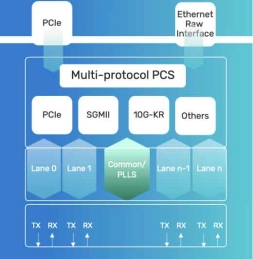

PHY for PCIe 4.0 - Low-power, long-reach, multi-protocol PHY for PCIe 4.0

- Wide range of protocols that support networking, high-performance computing (HPC), and applications

- Low-latency, long-reach, and low-power modes

- Multi-Link PHY—mix protocols within the same macro

- EyeSurf —non-destructive on-chip oscilloscope

- User-friendly graphical interface provides easy access to embedded bit-error-rate (BER) and pattern testers and monitors to measure the link performance in real time

-

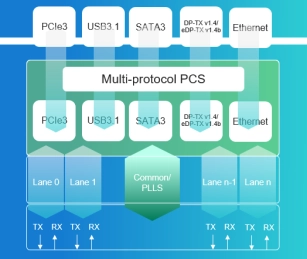

PHY for PCIe 3.1

- Supports PCIe 3.1, USB 3.1, DP-TX v1.4/eDP-TX v1.4b, SATA 3, 10G-KR and QSMII/SGMII

- Multi-protocol support for simultaneous independent links

- Supports SRIS and internal SSC generation

- Supports PCIe L1 sub-states

- Automatic calibration of on-chip termination resistors

- Supports internal and external clock sources with clock active detection

-

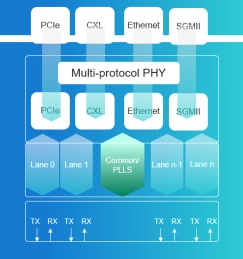

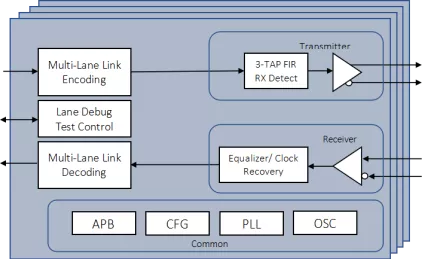

PHY for PCIe 5.0 and CXL

- Low-latency, long-reach, and low-power modes

- Wide range of protocols that support networking, storage, and computing applications

- Advanced equalization and clock-data-recovery to deliver unmatched channel loss handling performance and reliability

- Eye Surf —provides convenient access to an integrated non-destructive real-time eye scope and BER bathtub curve to monitor the bit error rate (BER) and the link performance during live traffic

-

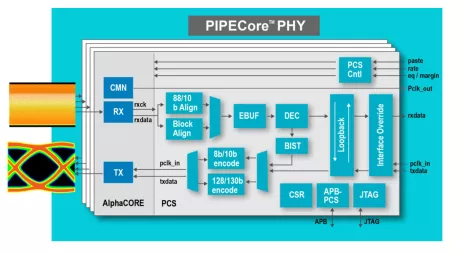

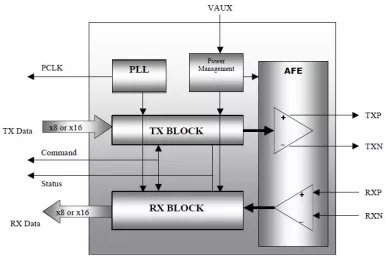

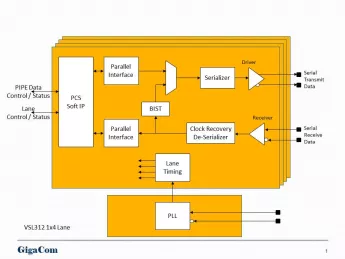

PCI Express PHY serial link PIPE Transceiver IP cell/hard macro

- Supports 2.5Gb/s serial data rate

- Utilizes 8-bit or 16-bit parallel interface to transmit and receive PCI Express data

- Full Support for Auxiliary Power (Vaux) for Energy aware systems like Multi-Port Host Controllers

- Data and clock recovery from serial stream on the PCI Express bus

-

PCIe Gen2 PHY

- PCI Express Gen 2 and Gen 1 compliant

- Supports various PCI Express modes and extensions

- Programmable amplitude and pre-emphasis

- Programmable receiver equalization

-

PCIe Gen3 PHY

- Low Risk - Silicon proven with Si characterization data

- Excellent Interoperability

- Superior Noise Immunity

-

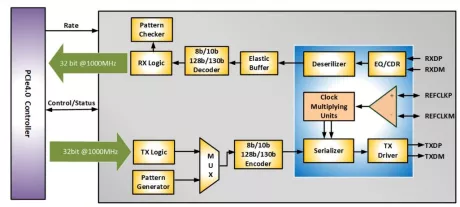

High Performance, Low Latency PCIe Gen5 PHY

- 8 lane PCIe 32/16/8/5/2.5 Gbps per lane

- Tight skew control of less than 1UI between lanes of the PMA