Cipher Accelerator IP for TSMC

Welcome to the ultimate Cipher Accelerator IP for TSMC hub! Explore our vast directory of Cipher Accelerator IP for TSMC

All offers in

Cipher Accelerator IP

for TSMC

Filter

Compare

17

Cipher Accelerator IP

for TSMC

from 3 vendors

(1

-

10)

-

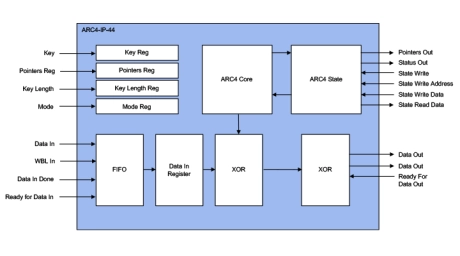

ARC4 Stream Cipher Accelerators

- The ARC4-IP-44 (EIP-44) is IP for accelerating the ARC4 stream cipher algorithm (used for legacy SSL & IPsec) up to 5 Gbps @ 600MHz.

- Designed for fast integration, low gate count and full transforms, the ARC4-IP-44 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high-speed crypto pipelines.

-

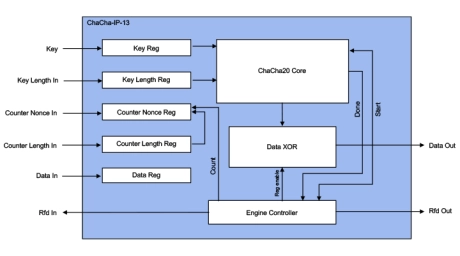

ChaCha20 Accelerators

- The ChaCha-IP-13 (EIP-13) is an IP solution for accelerating the ChaCha20 cipher algorithm (RFC7539), supporting the NIST CTR mode up to 12.8 Gbps @ 300MHz.

- Designed for fast integration, low gate count and full transforms, the ChaCha-IP-13 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high-speed crypto pipelines.

-

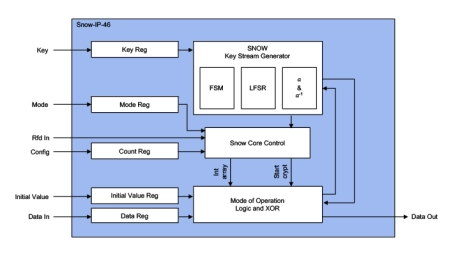

3GPP SNOW 3G Accelerators

- The SNOW-IP-46 (EIP-46) cipher accelerators implement the specification of the 3GPP Confidentiality and Integrity Algorithms as specified by 3GPP and ETSI.

- Designed for fast integration, low gate count and full transforms, the SNOW-IP-46 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high speed SoCs for base stations or other equipment requiring 3GPP support.

-

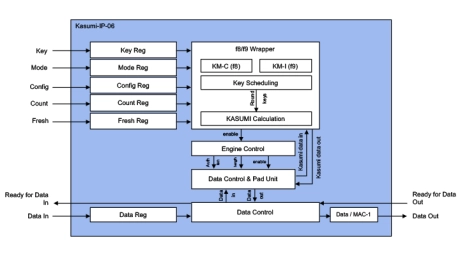

3GPP Kasumi Accelerators

- Wide bus interface (64-bit data, 128-bit keys) or 32-bit register interface.

- Includes key scheduling hardware.

- Modes Kasumi

- Algorithms f8 and f9.

- Fully synchronous design.

- Low Speed, High Speed versions.

-

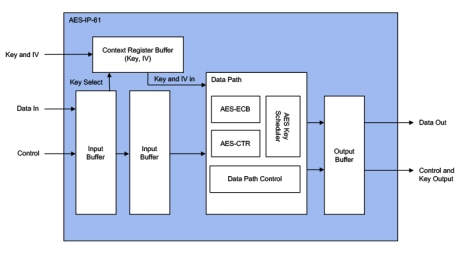

High speed low latency AES-GCM pipeline, 100Gbps

- The AES-IP-61 (EIP-61) is IP for accelerating AES-GCM based cryptographic solutions.

- Designed for easy integration and very high performance the AES-IP-61 crypto accelerator provide a reliable and cost-effective embedded IP solution that is easy to integrate into high-speed processing pipelines.

-

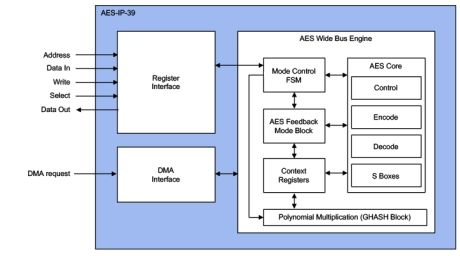

AES “All Modes” Accelerators

- The AES-IP-39 (EIP-39) is IP for accelerating the AES symmetric cipher algorithm (FIPS-197), supporting all NIST modes including ECB, CBC, CTR, CFB, OFB, CCM, GCM, CBC-MAC, CMAC, XTS, F8, F9 modes of operation up to 6.4 Gbps @ 1GHz.

- Designed for fast integration, low gate count and full transforms, the AES-IP-39 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into security modules needing versatile crypto.

-

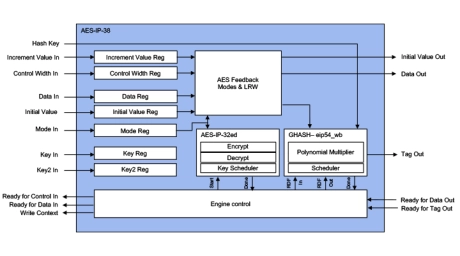

AES XTS/GCM Accelerators

- Wide bus interface

- Basic AES encrypt and decrypt operations

- Key sizes: 128, 192 and 256 bits

- Key scheduling in hardware, allowing key, key size and direction changes every 13/15/17 clocks with zero impact on throughput

- Hardware reverse (decrypt) key generation

-

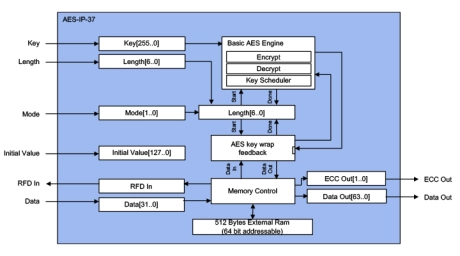

AES Key Wrap Accelerators

- Wide bus interface (128-bit data, 256-bit keys) or 32-bit register interface

- Key/KEK sizes: 128, 192 and 256 bits

- Includes key scheduling hardware

- Supported modes: NIST AES Key Wrap

- Memory interface for key, intermediate and result data storage up to 4096 bits (Maximum supported input data block size is 512 bytes)

-

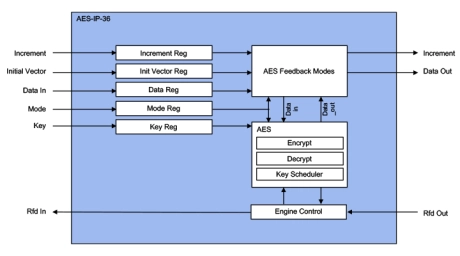

AES ECB/CBC/CTR Accelerators

- The AES-IP-36 (EIP-36) is IP for accelerating the AES symmetric cipher algorithm (FIPS-197), supporting ECB, CBC and CTR modes up to 12.8 Gbps @ 1GHz.

- Designed for fast integration, low gate count and full transforms, the AES-IP-36 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high speed crypto pipelines.

-

802.11i CCMP/TKIP IP Core

- Small size:

- Includes key lookup, encryption, decryption, header parsing and modification, key expansion and data interface

- Uses external memory for key storage;

- Configurable number of keys supported; 64 bytes are required per bidirectional link