MIPI D-PHY IP for TSMC

Welcome to the ultimate MIPI D-PHY IP for TSMC hub! Explore our vast directory of MIPI D-PHY IP for TSMC

All offers in

MIPI D-PHY IP

for TSMC

Filter

Compare

199

MIPI D-PHY IP

for TSMC

from 12 vendors

(1

-

10)

-

LVDS / sub-LVDS / DPHY TX - TSMC 6FFC

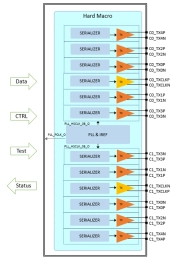

- The LVDS/Sub-LVDS/DPHY Combo TX converts parallel RGB data and 7/8/10 bits of CMOS parallel data into serial data streams.

- A phase-locked clock is transmitted in parallel with the data streams over a dedicated high-speed link.

- The polarity of differential signals for each data lane can be controlled.

-

MIPI D-PHY

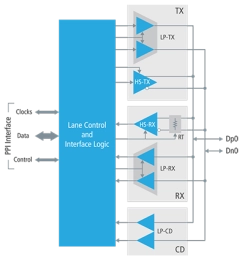

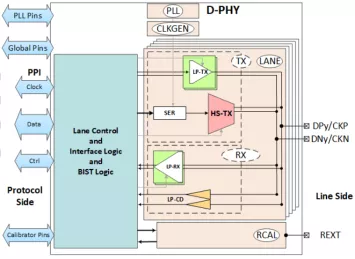

- Multiple Configurations Possible. TX-only (with integrated PLL), RX-only, and combined TX and RX configurations

- Complete Function for HS TX/RX, LP TX/RX, and LPCD with automatic termination control for high-speed and low-power modes

- Integrated BIST Capable of producing and checking PRBS, CRPAT, and CJTPAT

-

MIPI D-PHY IP 4.5Gbps in TSMC N7

- Supports MIPI Alliance Specification for D-PHY Version 2.5

- Consists of 1 Clock lane and 4 Data lanes

-

MIPI D-PHY Tx 4 Lanes - TSMC7FF18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Tx 2 Lanes - TSMC7FF18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 4 Lanes - TSMC7FF18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 2 Lanes - TSMC7FF18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Tx 4 Lanes - TSMC6ff18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Tx 2 Lanes - TSMC6ff18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 4 Lanes - TSMC6ff18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes