MIPI D-PHY Rx 4 Lanes - TSMC7FF18, North/South Poly Orientation

The D-PHY IP enables high-performance, low-power interface to SoCs, application processors, baseband processors, and peripheral d…

Overview

The D-PHY IP enables high-performance, low-power interface to SoCs, application processors, baseband processors, and peripheral devices for mobile, automotive, artificial intelligence (AI), and IoT applications. The PHY, for mainstream and FinFET processes, is compliant with the D-PHY specification, operating at 10Gb/s aggregate data rate in 4 lanes. Supporting low-power state modes allows the IP to deliver low-power consumption at the maximum speed to address the energy requirements of battery-operated devices. The D-PHY IP interoperates with the vendor’s CSI-2 and DSI/DSI-2 controllers which support key features of the latest MIPI display and camera specifications. The MIPI D-PHY IP is ASIL B Ready ISO 26262 certified, meeting the stringent requirements of automotive ADAS and Infotainment applications.

Key features

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

- Supports PHY Protocol Interface (PPI)

- Low-power escape modes and ultra low-power state modes

- Shutdown mode

- SCAN and loopback BIST modes

- Extensive access to internal programmability registers

- Primary, secondary, TX- and RX-only configurations

- Attachable PLL for primary applications

- Flexible input clock reference

- 50% DDR output clock duty cycle

- Silicon-proven, robust design available in advanced process technologies

- ASIL B Ready ISO 26262 certified for Grade 1 and Grade 2 automotive design

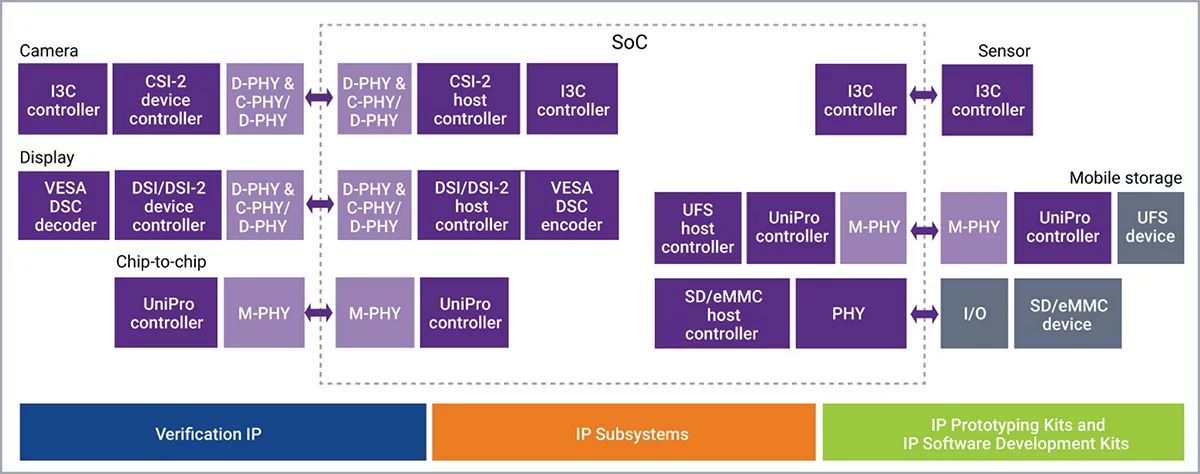

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 7nm | N7FF | — |

Specifications

Identity

Provider

Learn more about MIPI PHY IP core

MIPI DPHY Solution

Infineon Drives Automotive MCU Performance Higher with Synopsys Interface IP

Cadence First to Demo Complete M-PCIe PHY and Controller Solution at MIPI and PCI-SIG Conferences

Super Edge Medical SoC (SEMC)

D-PHY, M-PHY & C-PHY? First Look at Testing MIPI's Latest PHY

Frequently asked questions about MIPI PHY IP

What is MIPI D-PHY Rx 4 Lanes - TSMC7FF18, North/South Poly Orientation?

MIPI D-PHY Rx 4 Lanes - TSMC7FF18, North/South Poly Orientation is a MIPI PHY IP core from Synopsys, Inc. listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this MIPI PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.