Interconnect IP for TSMC

Welcome to the ultimate Interconnect IP for TSMC hub! Explore our vast directory of Interconnect IP for TSMC

All offers in

Interconnect IP

for TSMC

Filter

Compare

810

Interconnect IP

for TSMC

from 38 vendors

(1

-

10)

-

MIPI C-PHY/D-PHY Combo RX+ IP 4.5Gsps/4.5Gbps in TSMC N5

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHY mode

-

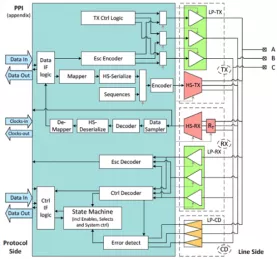

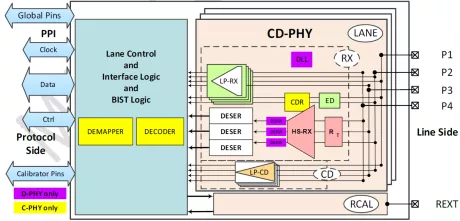

MIPI D-PHY / C-PHY Combo IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- Compliant to MIPI Alliance Standard for C-PHY specification Version 1.2

- Compliant to MIPI Alliance Standard for D-PHY specification Version 1.2

-

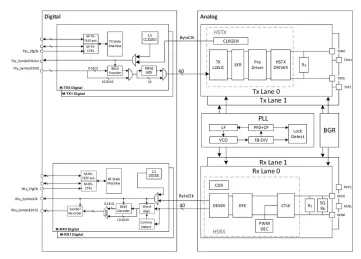

Multiprotocol SerDes PMA

- Supports over 30 protocols including CEI 6G & 11G SR, MR, LR, Ethernet 10GBASE-X/S/K/R, PCIe Gen1/2/3/4, V-by-One HS/US, CPRI, PON, OTN/OTU, 3GSDI, JESD204A/B/C, SATA1-3, XAUI, SGMII

- Programmable (De)Serialization width: 8, 10, 16, 20, 32, or 40 bit

- Tx ring PLL includes fractional multiplication, spread spectrum and Jitter Cleaner function for Sync-E and OTU

- Core-voltage line driver with programmable pre-and post-emphasis

-

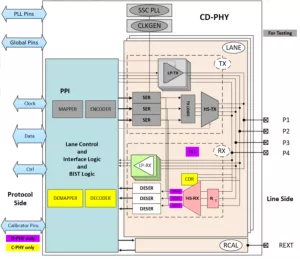

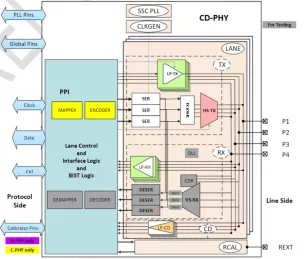

MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- Compliant to MIPI for C-PHY specification Version 1.2

- Compliant to MIPI for D-PHY specification Version 1.2

-

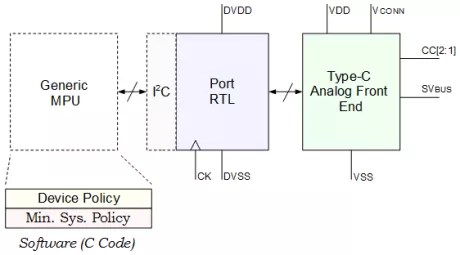

Complete USB Type-C Power Delivery IP

- Mixed signal Analog Front End Macros for 65n, 130n, 150nm, and 180n technologies.

- RTL code from AFE to I2C compatible register set.

- Stand alone C code for Protocol, Device Policy Manager, and System Policy Manager.

- IP demonstration & development board, with compliance reports.

- Full chip integration of USB Type-C, and associated software.

-

MIPI C-PHY/D-PHY Combo TX+ IP 4.5Gsps/4.5Gbps in TSMC N5

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHY mode

-

MIPI C-PHY/D-PHY Combo RX IP 4.5Gsps/4.5Gbps in TSMC N7

- Dual mode PHY Supports MIPI Alliance Specification D-PHYv2.5 & C-PHYv2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHYmode

-

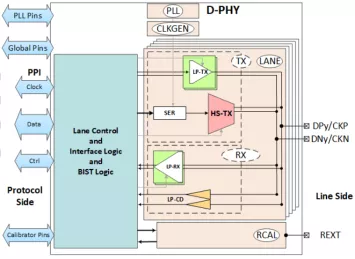

MIPI D-PHY IP 4.5Gbps in TSMC N7

- Supports MIPI Alliance Specification for D-PHY Version 2.5

- Consists of 1 Clock lane and 4 Data lanes

-

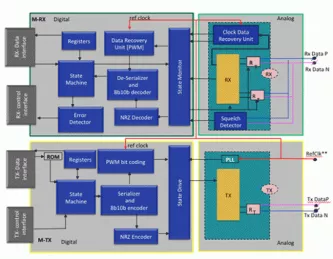

MIPI M-PHY G4 Designed For TSMC 28nm HPC+

- Compliant to MIPI Alliance Standard for M-PHY specification Version 4.1

- Supports M-PHY Type-I system

- Support for Clock and Data Recovery Options

-

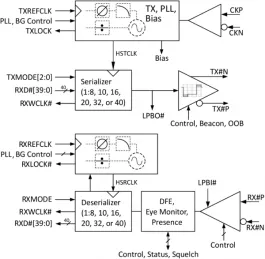

MIPI M-PHY HS-G4 IP (M-PHY v4.1) in TSMC 40G

- Supports MIPI® Alliance Specification for M- PHY® Version 4.1.

- Dual-simplex point-to-point interface with ultra-low voltage differential signaling.

- Slew-rate control for EMI reduction.