Interconnect IP for Tower

-

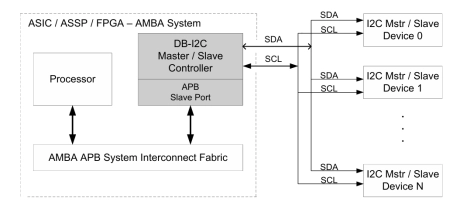

I2C Controller IP- Master / Slave, Parameterized FIFO, APB Bus

-

The Digital Blocks DB-I2C-MS-APB Controller IP Core interfaces a microprocessor via the AMBA APB Bus to an I2C Bus in Standard-Mode (100 Kbit/s) / Fast-Mode (400 Kbit/s) / Fast-Mode Plus (1 Mbit/s) / Hs-Mode (3.4+ Mb/s) / Ultra Fast-Mode (5 mbit/s).

The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

The DB-I2C-MS-APB is a Master/Slave I2C Controller that in Master Mode controls the Transmit or Receive of data to or from slave I2C devices while in Slave Mode allows an external I2C Master device to control the Transmit or Receive of data.

-

-

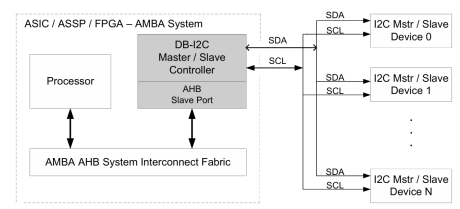

I2C Controller IP- Master / Slave, Parameterized FIFO, AHB Bus

-

The DB-I2C-MS-AHB Controller IP Core interfaces a microprocessor via the AMBA AHB Bus to an I2C Bus in Standard-Mode (100 Kbit/s) / Fast-Mode (400 Kbit/s) / Fast-Mode Plus (1 Mbit/s) / Hs-Mode (3.4+ Mb/s) / Ultra Fast-Mode (5 mbit/s).

The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

The DB-I2C-MS-AHB is a Master / Slave I2C Controller that in Master Mode controls the Transmit or Receive of data to or from slave I2C devices while in Slave Mode allows an external I2C Master device to control the Transmit or Receive of data.

-

-

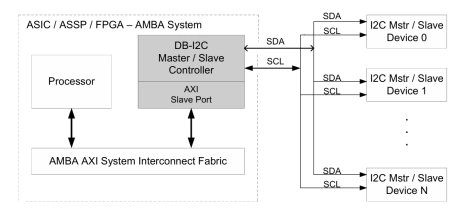

I2C Controller IP- Master / Slave, Parameterized FIFO, AXI Bus

- The DB-I2C-MS-AXI Controller IP Core interfaces a microprocessor via the AMBA AXI Bus to an I2C Bus in Standard-Mode (100 Kbit/s) / Fast-Mode (400 Kbit/s) / Fast-Mode Plus (1 Mbit/s) / Hs-Mode (3.4+ Mb/s) / Ultra Fast-Mode (5 mbit/s).

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

- The DB-I2C-MS-AXI is a Master / Slave I2C Controller that in Master Mode controls the Transmit or Receive of data to or from slave I2C devices while in Slave Mode allows an external I2C Master device to control the Transmit or Receive of data.

-

I2C Controller IP – Master, Parameterized FIFO, AXI Bus

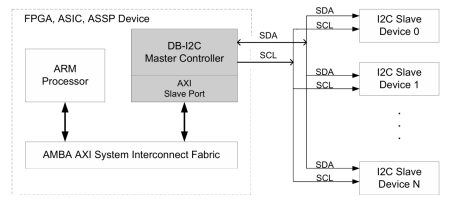

- The DB-I2C-M-AXI Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high performance microprocessor via the AMBA 2.0 AXI System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

- The DB-I2C-M-AXI is a Master I2C Controller that controls the Transmit or Receive of data to or from slave I2C devices. Figure 1 depicts the system view of the DB-I2C-M AXI Controller IP Core embedded within an integrated circuit device.

-

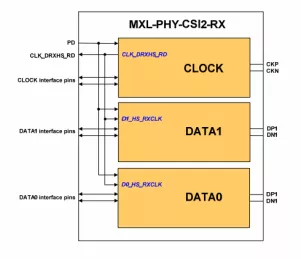

MIPI D-PHY CSI-2 RX (Receiver) IP

- Consists of 1 Clock lane and 2 Data lanes

- Complies with MIPI Standard 1.0 for D-PHY

- Supports both high speed and low-power modes

- 80 Mbps to 1Gbps data rate in high speed mode

-

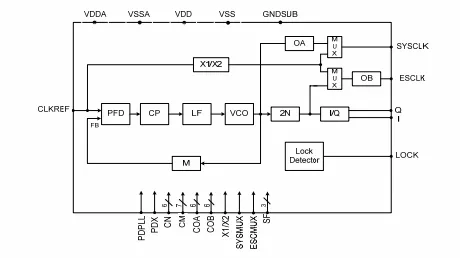

MIPI PLL

- All output programmable dividers produce 50% duty cycle for both even and odd divisors

- High performance, highly programmable MIPI Pixel PLL

- Digital CMOS process

- Low power dissipation

-

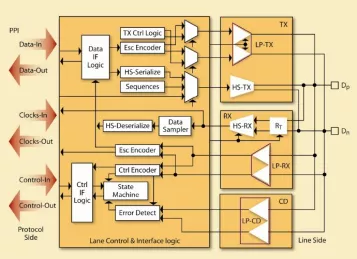

MIPI D-PHY Universal IP

- Complies with MIPI Standard for D-PHY V1.0

- Point-to-point differential interface supporting multiple data lanes and a clock lane

- Supports both high speed and low-power modes

- Data lanes support both bidirectional and unidirectional modes