The Arasan USB 2.0 Hub IP core is an USB 2.0 specification compliant hub core

that supports 480 Mbit/s in High Speed (HS) mode, 12 Mbit/s in Full Speed (FS)

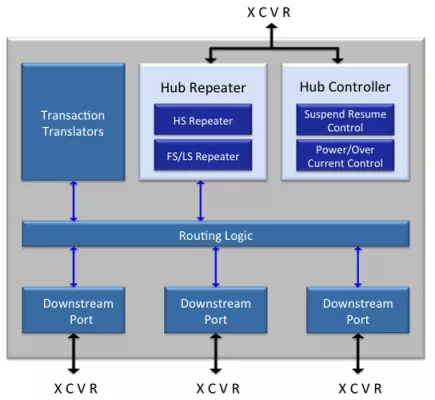

mode, and 1.5 Mbit/s in Low Speed (LS) mode. The Arasan USB 2.0 Hub IP core consists of the Hub Controller, Hub Repeater, Transaction Translators, Routing Logic, and Downstream Ports.

The Hub Controller controls the operation of the USB hub by interpreting both the USB commands and Hub class specific commands. High-speed packets originated from the root hub are forwarded by the Hub Repeater to the HS Downstream Ports through the Routing Logic. Full-speed and low-speed packets scheduled by the host system software as split transactions are forwarded to the Transaction Translators. The Transaction Translators handle split transactions that convey isochronous, interrupt, control, and bulk transfers across the high-speed bus to and from the full-speed and low-speed devices that attached to the hub. The Transaction Translators also perform CRC on incoming packets from the Hub Repeater or Routing Logic. The Routing Logic connects the Hub Repeater to the Downstream Ports in a high-speed transfer, and it connects the Transaction Translators to the Downstream Ports in a full-speed or low-speed transfer. The number of Downstream Ports is scalable.

The Arasan Auto-configure and Auto-wire are pre-compiled C language utilities that allow users to have the freedom to fully customize their designs.

USB 2.0 Hub Controller

Overview

Key Features

- High speed support: 480 Mbit/s

- Full speed support: 12 Mbit/s

- USB 2.0 Compliant

- High/Full speed support using 8/16 bit UTMI/ULPI interface

- Master DMA implementation for each endpoint

- Optional PIO Mode for each endpoint (can be used for Interrupt endoints)

- System bus Master/Target clock

- UTMI Interface Clock: 30/60 MHz

- Endpoint Configuration

- Configurable up to 15 Tx and Rx endpoints

- Configuration options: Bulk, control, isochronous, interrupt

- Dedicated control endpoint zero

- Configurable dual port RAM shared between endpoints

- USB Suspend/Resume support

- 32/64 bit AXI, AHB or OCP bus interfaces

Benefits

- Fully compliant to USB 2.0 specifications

- Highly flexible and configurable

- Ideal for easy and cost-effective device integration

- Premier direct support from Arasan IP Engineering Team

Block Diagram

Deliverables

- RMM-compliant synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

- Simulation scripts

Technical Specifications

Maturity

Silicon proven

Availability

Now