Ultra Low Power SAR ADC - TSMC, 40LP

Overview

The ADC8B125NMsps is an ultra-low power SAR ADC with a sampling frequency of 125MHz.

Key Features

- TSMC 40 LP ( SVT )

- -40 to 125 Deg C

- Ultra Low Power 3.5 mW

- Sampling Frequency of 125 MHz

- Input Voltage 1V

- Analog Bandwidth ( BW ) 62.5 MHZ

- Signal to Noise and Distortion Ration

- 43.8 dB ( Fs= 125MHZ, Vin = 1Vpp, @62.5 MHz )

- Data Latency ( Fs=125 MHz ) 4 cycles

- Input Capacitance Cin ( Dynamic @ Sampling ) 500 fF

- Diff. Nonlinearity DNL +/- 0.5 LSB

- Integ. Nonlinearity INL +/- 1 LSB

- Supply Voltage Vdd 1.2 V

- Power Dissipation Pd ( Typ ) 3.5 mW

- Area 0.1mm2

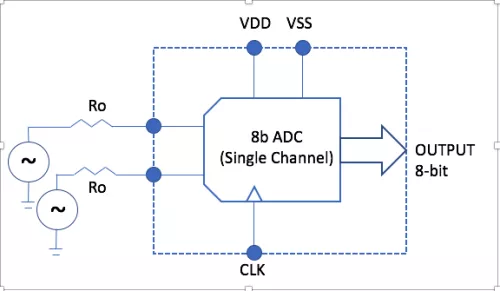

Block Diagram

Applications

- IOT

- Serial Links

- Wireless communications

Deliverables

- User Guide

- Characterization Report

- CDL netlist

- Layout in GDS2 format

- LEF view

- .LIB view

- Verilog model

Technical Specifications

Foundry, Node

TSMC, 40LP

Maturity

Silicon Proven

Availability

Immediate

TSMC

Pre-Silicon:

40nm

LP