Single Port SRAM Compiler GlobalFoundries 55LPx Ultra-high density, low power, up to 320K bits

Overview

Proven Single Port SRAM compiler for GF55 LPx - Memory optimized for ultra high density and high speed with compiler range up to 320K bits

Key Features

- Capacity to 320K bits

- Word width: 8 to 144 bits

- Address range: 32 to 8k

- Nominal voltage: 1.2V

- Retention voltage: 0.6V

- Configuration

- HVT/SVT for memory periphery

- HVT for the memory core

- Designed with 4 metal layers, routing enabled over the memory in metal 4 within free routing tracks

- Migration on an existing architecture already available for other processes

- Smart periphery design to reach the highest density

- Up to 20% denser than standard memory compilers at 55 nm

- Ultra low leakage design

- Multiple power mode enabling several tradeoff between leakage savings and wake up time

- Stand by mode

- Nap mode enabling up to 75% savings compared to stand by mode and only one clock cycle to wake up

- Low dynamic power

- Up to 50% less power consuming than alternative solutions

- Partitioned array

- Variable write-mask capability

- Easy integration

- MUX options

- Data range flexibility allows easy addition of bits for redundancy or ECC purposes

- Address range flexibility allows easy addition of single rows for redundancy purposes

- Complete mismatch validation of the memory architecture taking into account local and global variation

- Optional BIST for industrial test for fabricated instances

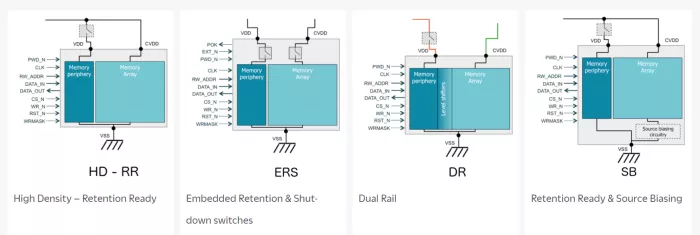

Block Diagram

Technical Specifications

Foundry, Node

GlobalFoundries 55nm LPx

Maturity

In Production

Availability

Now

Related IPs

- Single Port SRAM compiler - Memory optimized for ultra high density and low power - 3ML- compiler range up to 320 k

- Single Port SRAM compiler - Memory optimized for high density and low power - Deep N Well supported - compiler range up to 320 k

- Single Port SRAM compiler - Memory optimized for high density and speed - Dual Voltage - Compiler range up to 640 kbits

- Single Port SRAM compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 320 k

- Single Port SRAM compiler - Memory optimized for high density and low power - compiler range up to 640 k

- Single Port SRAM compiler - Memory optimized for high density and low power - compiler range up to 320 k