Quadrature Amplitude Modulation IP

Welcome to the ultimate Quadrature Amplitude Modulation IP hub! Explore our vast directory of Quadrature Amplitude Modulation IP

All offers in

Quadrature Amplitude Modulation IP

Filter

Compare

19

Quadrature Amplitude Modulation IP

from 10 vendors

(1

-

10)

-

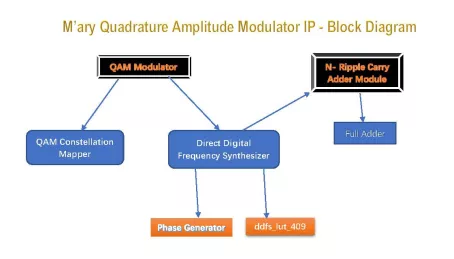

M’ary Quadrature Amplitude Modulator IP in VHDL, FPGA and SDR

- Fully verified and synthesized with source code and netlist, integration guide, license and manual

-

Quadrature Amplitude Modulation: Modulator and Demodulator

- 1. Quadrature amplitude modulation Aside from increased channel capacity, QAM has various other advantages, which are stated below.

- 2. One of the most significant advantages of QAM is its ability to sustain a high data rate. As a result, the carrier signal can carry a certain amount of bits. Because of these benefits, it is preferred in wireless communication networks.

- 3. The noise immunity of QAM is quite strong. Noise interference is a bit low as a result of this.

- 4. It has a low mistake probability value.

-

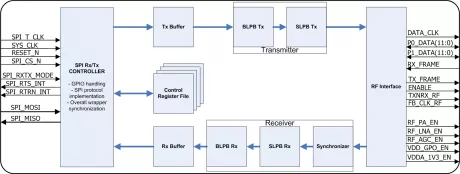

OFDM Baseband Processor

- Customized transmit and receive physical layer chains.

- Fully synchronous design enabling high throughput TDD operation.

-

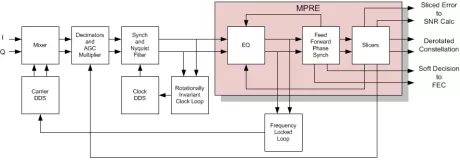

Mobile Phase Recovering Equalizer

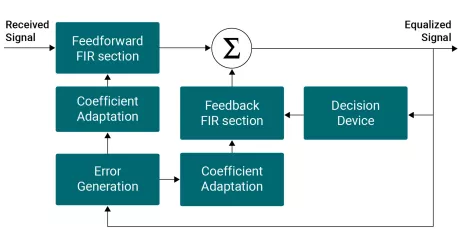

- 17-tap complex-arithmetic LMS Channel Equalizer with adaptation bandwidth and leakage rate control as well as independent coefficient hold and reset controls

- VV4 Quasi-Coherent Demodulator for signal phase recovery and differential detection

- Integrated Symbol Slicer provides demodulated soft-decision outputs

- AGC output controls in proportional and up/dn format for constant-modulus and phase-locked processing

-

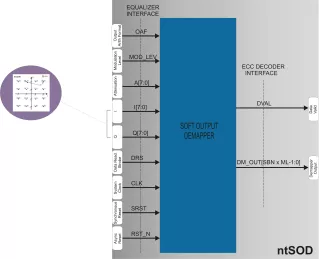

Configurable Soft Output Demapper

- Soft output demapper based on the LLR (Log Likelihood Ratio)algorithm.

- Parameterized number of soft bits per symbol .

- Parameterized architecture depending on supported modulation levels for optimum resources utilization.

- Programmable modulation level.

-

MMSE MIMO Detector

- Adaptable to different transmitter/receiver antenna configurations (e.g., 2×2, 4×2 or 4×4).

- Support for different modulation schemes at run-time (QPSK, 16-QAM, 64-QAM, 256-QAM)

- QR decomposition included

-

High Performance VSB/QAM Demodulator Core

- Input interface supports standard IF, low IF, and zero IF tuners.

- 12-bit data interface provides dynamic range needed for effective suppression of adjacent channel interference.

- Digital SAW filter reduces external part count.

- Robust, proprietary acquisition algorithm for better than 100 millisecond acquisition time over a wide range of inputs.

-

ISDB-T Demodulator

- Full 13-segment ISDB-T demodulator

- ARIB STD-B31 compliant supporting 1, 2 or 3-layers

- High-performance demodulation engine for demanding applications

- Sophisticated channel impairment correction

-

High Data Rate Modulator

- Versatile digital modulation engine

- Programmable constellation mapper supports multiple constellations from BPSK to 256QAM

- Supports offset-QPSK (OQPSK)

- Supports continuously variable symbol rates

-

High Data Rate Enhanced Demodulator

- Versatile digital demodulation engine supporting BPSK, QPSK, offset-QPSK (OQPSK), 8PSK, 8QAM* (three variants), 16QAM, 32/64QAM (HDRM-D2 core only) & 16/32APSK (HDRM-D2 core only)

- Close to theoretical performance

- Option to increase datapath resolution to help cope with elevated levels of adjacent carrier interference (HDRM-D2 core only)

- N-stage symbol rate blind adaptive equaliser option reduces linear channel distortions such as multipath (HDRM-D2 core only)