Overview

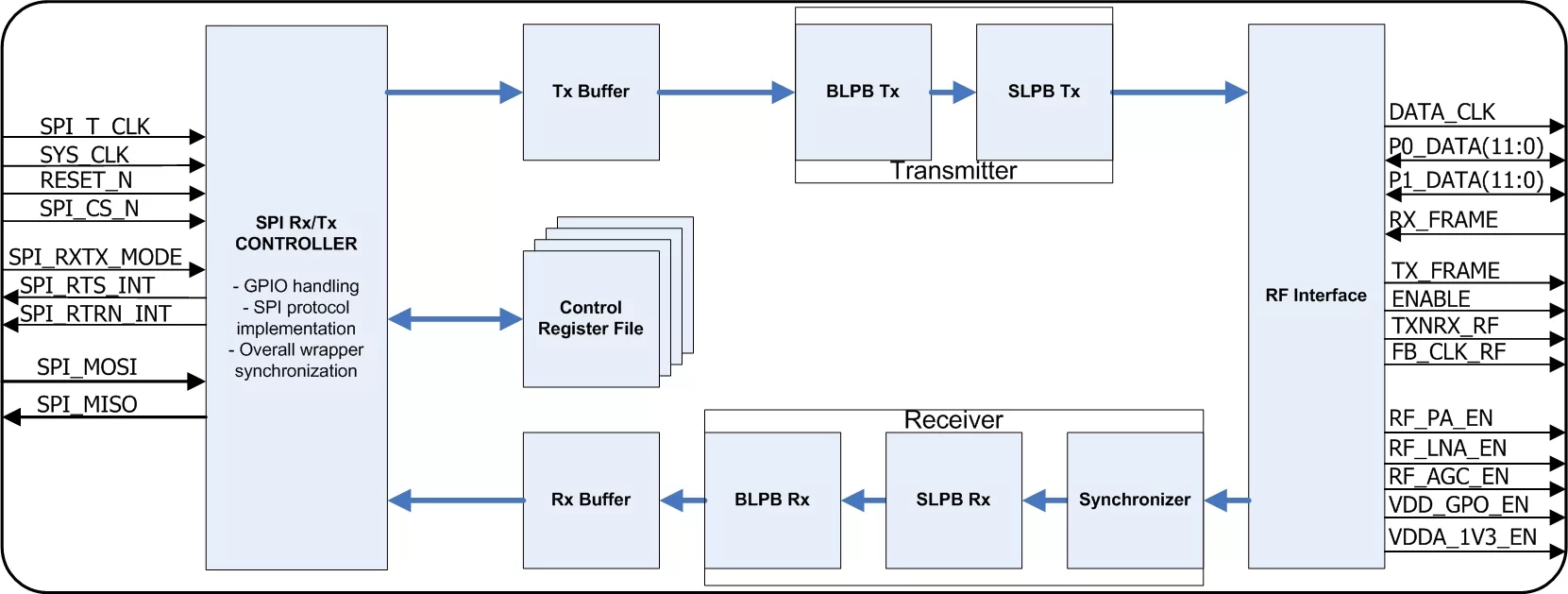

Noesis Technologies ntOFDM_BBP is a custom baseband processor, which implements the physical layer of an OFDM, time division duplexing (TDD) system. The baseband processor includes both transmission and reception bit-level and symbol-level processing chains including a sophisticated synchronization unit. The host interface is based on SPI protocol as well as with handshaking/interrupt ports. This custom system implements a subset of 802.16d standard functional options/features and is highly configurable via the integrated register file. An RF interface module is also included, compatible with Analog Devices AD9361 RF transceiver.

The Bit-level processing block (BLPB) transmission chain implements the following functional units : randomization, FEC encoding, interleaving and symbol mapping. In BLPB reception chain the following operations are implemented: soft symbol demapping, deinterleaving, FEC decoding and derandomization. The FEC module is based on the implementation of the Reed Solomon algorithm.

The Symbol-level processing block (SLPB) transmission chain implements the following functional units: OFDM symbol transmitter, IFFT , CP insertion. In reception chain the SLPB module is preceded by the synchronization unit, which is searching for known preamble values in order to locate the start an incoming wimax sub-frame. Once the sub-frame is located, frequency offset compensation is applied and received information is propagated down to SLPB reception chain. In SLPB reception chain the following operations take place: CP removal, FFT, OFDM symbol receiver, channel estimation, phase offset compensation and channel equalization.

Learn more about Cellular IP core

Chet Babla, ARM

By Hantro

SATCOM is adopting 3GPP 5G NTN standards to scale beyond proprietary silos, enabling interoperable satellite networks and global direct‑to‑cell services.

Ceva’s 2025 Technology Symposium series, held in Shanghai, Hsinchu and Herzliya , brought together a global community of engineers, product leaders, and ecosystem partners. Each location had its own flavor, but a single theme ran through every discussion: how to bring meaningful intelligence to the edge of every device.