USB 2.0 Hub IP

Filter

Compare

38

IP

from

14

vendors

(1

-

10)

-

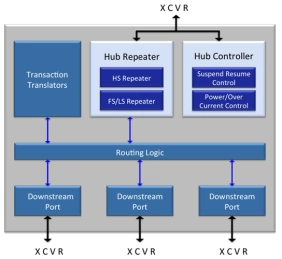

USB 2.0 Hub IP Core

- The USB 2.0 Hub IP core is a USB 2.0 specification compliant hub core that supports 480 Mbit/s in High Speed (HS) mode, 12 Mbit/s in Full Speed (FS) mode, and 1.5 Mbit/s in Low Speed (LS) mode.

- The USB 2.0 Hub IP core consists of the Hub Controller, Hub Repeater, Transaction Translators, Routing Logic, and Downstream Ports.

-

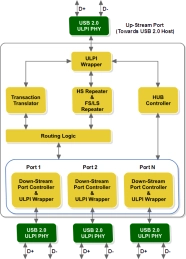

USB 2.0 HUB (USB20HUB)

- The USB 2.0 Hub IP core provides a link between the USB2.0 Host and multiple USB peripherals via UTMI + Low pin interface (ULPI).

- It supports High speed, Full speed and Low speed peripheral devices.

- Its rich features and ease of use makes it more suitable for embedded applications.

-

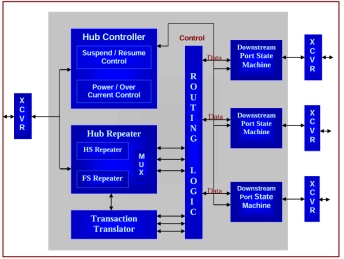

USB 2.0 Hub Controller

- The USB 2.0 Hub core consists of Hub Controller, Repeater and Transaction Translator.

- The Hub Controller provides the mechanism for host to hub communication.

- Hub-specific status and control commands permit the host to configure a hub and to monitor and control its transaction translator individual downstream ports.

-

USB 2.0 PHY IP core

- Complies with USB specifications, rev. 2.0 and 1.1

- Complies with UTMI+ specification, level 3, rev. 1.0

- Supports 480Mb/s (HS), 12Mb/s (FS) and 1.5MB/s (LS) serial data transmission rates

- Supports 8-bit unidirectional Parallel Interface Engine (PIE) bus for HS, FS and LS modes, and Serial Interface Engine (SIE) for FS and LS modes

-

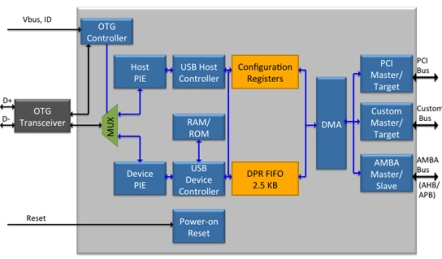

USB 2.0 OTG IP Core

- High speed support: 480 Mbit/s

- Full speed support: 12 Mbit/s

- USB 2.0 Compliant

- High/Full speed support using 8/16 bit UTMI/ULPI interface

-

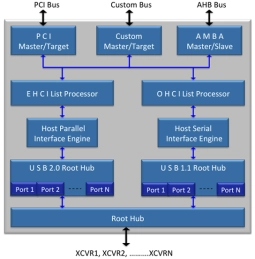

USB 2.0 Host IP Core

- The USB 2.0 Host IP is a USB 2.0 specification compliant host IP core with an optional AHB, PCI, or custom host interface.

- The USB 2.0 Host IP supports 480 Mbit/s in High Speed (HS) mode. 12 Mbit/s in Full Speed (FS) mode, and 1.5 Mbit/s in Low Speed (LS) mode.

-

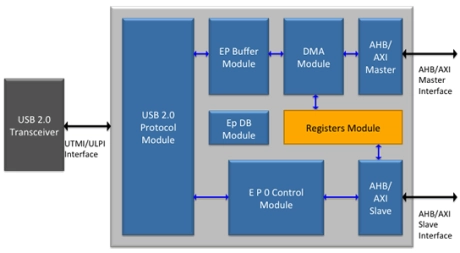

USB 2.0 Device IP Core

- High speed support: 480 Mbit/s

- Full speed support: 12 Mbit/s

- USB 2.0 Compliant

- High/Full speed support using 8/16 bit UTMI/ULPI interface

-

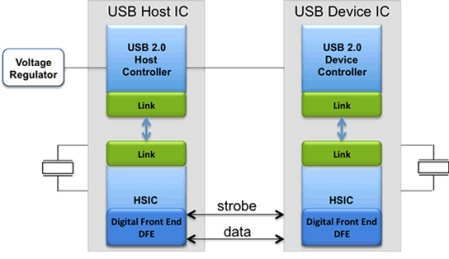

High Speed Inter-CHIP USB 2.0 PHY

- High-Speed 480Mbps data rate only

- Source-synchronous serial interface

- No power consumed unless a transfer is in progress.

- Maximum trace length of 10cm

-

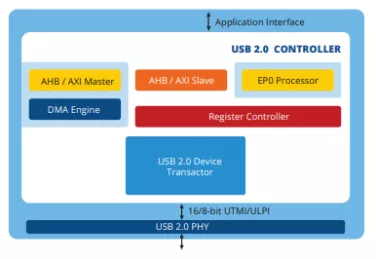

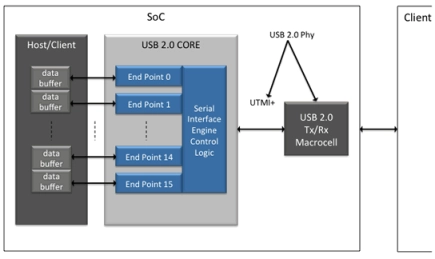

USB 2.0 Device Controller IP

- The USB 2.0 device controller can be configured to support all types of USB transfers – bulk, interrupt and isochronous. While operating in device mode, it can be dynamically configured to support a configurable number of endpoints, interfaces, alternate interfaces, and settings.

- The USB 2.0 device controller can be configured to support any combination of USB 2.0 interface speeds – LS (1.5 Mbps), FS (12.0 Mbps), HS (480 Mbps). Sample combinations are LS only, FS only, HS only, LS and FS, and FS and HS.

- The USB 2.0 device controller supports all low-power features of USB specifications, including suspend, remote wakeup and Link Power Management states – L1, L2.

- The USB 2.0 device controller supports all test modes features, a requisite for obtaining USB-IF certification