JEDEC UFS IP

Filter

Compare

50

IP

from

7

vendors

(1

-

10)

-

-

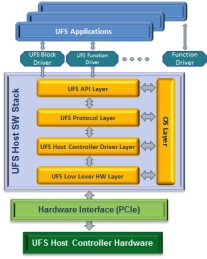

UFS 2.1 Stack & Driver

- Compliant with JEDEC UFS HCI 2.0 and MIPI UniPro Specification version 1.6

- Portability in choice of OS, processors and hardware

- Easy-to-use interface for applications

- Fully documented generic device operation API

-

UFS Hardware Validation Platform (HVP)

- Compliant to JEDEC UFS 1.0, HCI 1.0, UniPro 1.40

- Available in Host and Device configuration

-

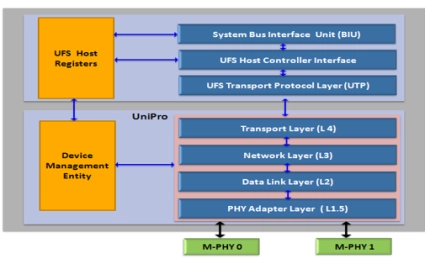

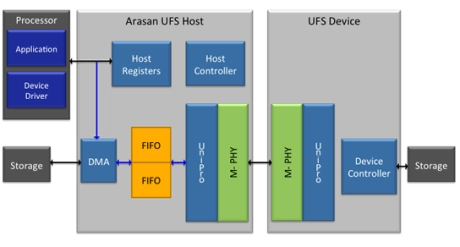

UFS 2.1 Host Controller IP

- JEDEC UFS 2.0 and UFS HCI 2.0 Compliant

- Supports high performance M-PHY v3.0 type-1

- 2 lanes @ 5.9 Gbps per lane

- UniPro v1.6 link layer

- Definable write-protect group size

-

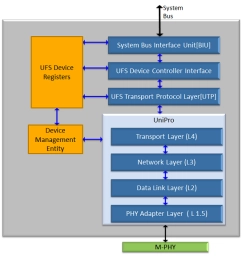

UFS 2.1 Device Controller IP

- The UFS 2.1 Device controller uses an M-PHY® 3.1 Adapter Layer backed by a UniPro v1.6 Link layer controller as per the specification.

- The UFS compliant IP cores are interface building blocks that simplify interconnect architectures in mobile platforms.

-

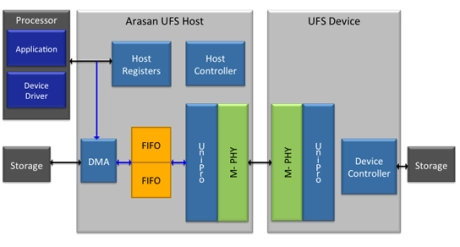

UFS 3.0 Device

- UFS 3.0 is the next specification update pending from JEDEC.

- Arasan will offer UFS 3.0 compatible Host and Device Controllers in late Q2 2017 to select customers.

-

UFS 4.0 Host

- UFS 4.0 (JESD220F.pdf)

- UFS HCI 4.0 (JESD223E.pdf)

- MIPI UniPro version 2.0(mipi_UniPro_specification_v2-0.pdf)

- MIPI M-PHY version 5.0(mipi_M-PHY_specification_v5-0.pdf)

-

UFS 3.1 Device

- UFS 3.1 is the next specification update pending from JEDEC.

- Arasan will offer UFS 3.1 compatible Host and Device Controllers in late Q2 2017 to select customers.

-

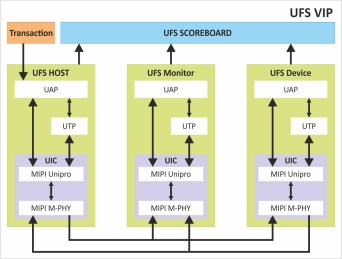

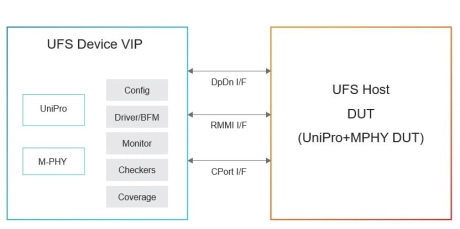

Simulation VIP for UFS

- Interfaces

- DPDN I/F and RMMI I/F when used with UniPro VIP. CPort signaling pin I/F and CPort message using transactions

- UTP Layer - UPIUs

- NOP IN, NOP OUT, Query Request/ Response, Task Management Request/ Response, Command, Response, Data Out, Data In

-

UFS Verification IP

- Supports both host and device system.

- VIP comes with UFS interconnect.

- VIP’s UFS application layer, transport protocol layer and interconnect layer can also be replaced or use as a BFM standalone.

- Supports of logical units, as well as well-known logical units.