eMMC IP

Welcome to the ultimate eMMC IP hub! Explore our vast directory of eMMC IP

All offers in

eMMC IP

Filter

Compare

54

eMMC IP

from 12 vendors

(1

-

10)

-

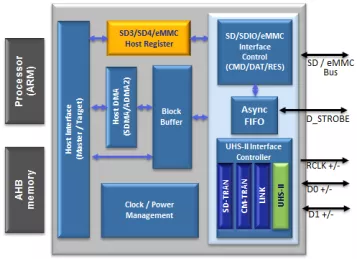

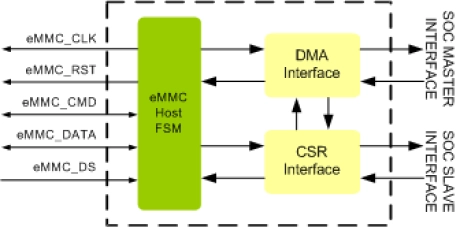

eMMC 5.1 Host Controller

- Compliant with eMMC Specification Version 5.0

- Supports one of the following System/Host Interfaces: AHB, AXI or OCP

-

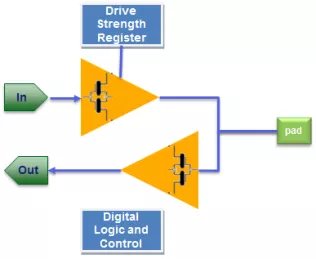

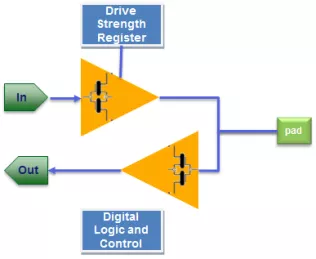

eMMC 5.1 HS400 PHY and I/O Pads in TSMC 28HPM-NS

- Silicon proven, fully compliant core

- Premier direct support from IP core designers

- Easy-to-use industry standard test environment

-

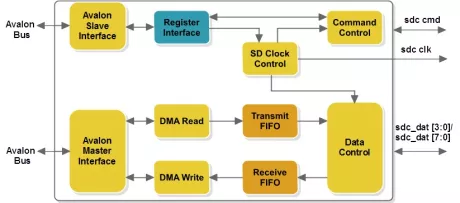

SD/eMMC Host Controller

- Supports selection between SD and eMMC

- Supports CRC7 and CRC16 generation and verification on Hardware

- Supports multiple block transfer

-

eMMC 5.1 HS400 PHY and I/O Pads in TSMC 28HPM-EW

- • Suitable for Transmitter, Receiver, and Data Strobe pins

- VCORE Pre driver voltage

- VCCQ Post driver voltage

- TJ Junction temperature

-

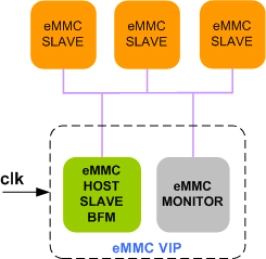

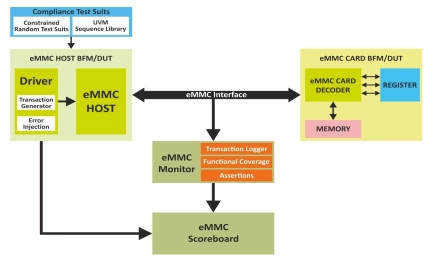

eMMC Verification IP

- Supports eMMC standard JESD84-A441, JESD84-B45, JESD84-B50, JESD84-B51 and JESD84-B51A specification.

- Supports stream transfer operations.

- Supports three different data width bus modes

- 1-bit(default)

-

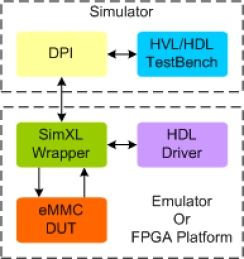

eMMC Synthesizable Transactor

- Supports eMMC standard JESD84-A441, JESD84-B45, JESD84-B50, JESD84-B51 and JESD84-B51A specification.

- Supports stream transfer operations.

- Supports three different data width bus modes

- 1-bit(default)

-

eMMC Host Controller IIP

- Compliant with JESD84-B50 Specification and earlier versions

- Compliant with JEDEC eMMC CQHCI for Command Queuing

- SD host controller Specification 6.0 compliant

- Supports different data bus width modes : 1-bit, 4-bit, 8-bit.

-

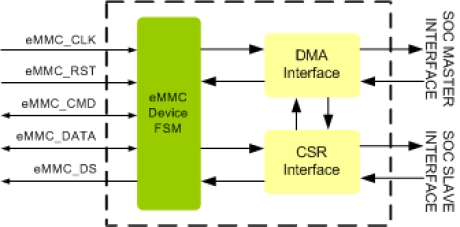

eMMC Device Controller IIP

- Compliant with JESD84-B51 Specification and earlier versions

- Compliant with JEDEC eMMC CQHCI for Command Queuing

- Supports different data bus width modes : 1-bit, 4-bit, 8-bit.

- Supports Command queuing

-

eMMC v5.1/A Verification IP

- Compliant with JEDEC eMMC version JESD84 - B51 and JESD84 – B51A.

- Supports eMMC devices from all leading vendors.

- Supports configuration for both host and device.

- Support all data widths 1x, 4x, and 8x.

-

TSMC N3P 1.8V IO Platform supporting cells

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution