eMMC PHY IP

Welcome to the ultimate eMMC PHY IP hub! Explore our vast directory of eMMC PHY IP

All offers in

eMMC PHY IP

Filter

Compare

39

eMMC PHY IP

from 7 vendors

(1

-

10)

-

eMMC 5.1 HS400 PHY and I/O Pads in TSMC 28HPM-NS

- Silicon proven, fully compliant core

- Premier direct support from IP core designers

- Easy-to-use industry standard test environment

-

eMMC 5.1 HS400 PHY and I/O Pads in TSMC 28HPM-EW

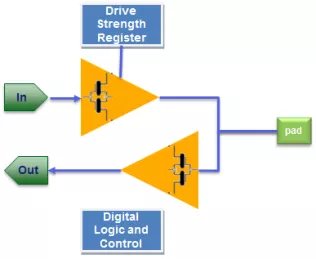

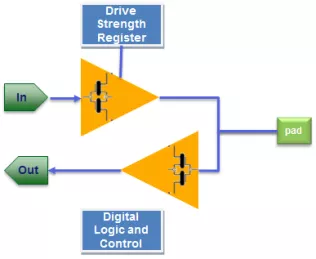

- • Suitable for Transmitter, Receiver, and Data Strobe pins

- VCORE Pre driver voltage

- VCCQ Post driver voltage

- TJ Junction temperature

-

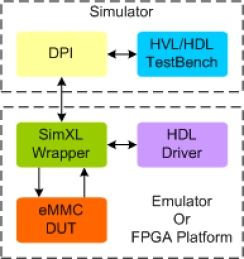

eMMC Synthesizable Transactor

- Supports eMMC standard JESD84-A441, JESD84-B45, JESD84-B50, JESD84-B51 and JESD84-B51A specification.

- Supports stream transfer operations.

- Supports three different data width bus modes

- 1-bit(default)

-

TSMC N3P 1.8V IO Platform supporting cells

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

TSMC N3P SD/eMMC PHY North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

SD/eMMC - TSMC 7FF, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

SD/eMMC - TSMC 6FF, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

SD/eMMC - TSMC 28HPM, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

SD/eMMC - TSMC 28HPCP, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

TSMC 22ULL 1.8V/3.3V SD/eMMC PHY AG2

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution