Silvaco’s Ultra High-Speed cache memory is an adaptable,

independent, non-coherent cache Intellectual Property

(IP) featuring an advanced cache architecture. This

architecture enhances system performance, scalability,

power efficiency, data locality, application responsiveness,

cost optimization, and market competitiveness, providing

a distinctive business value.

Ultra High-Speed Cache Memory Compiler

Overview

Key Features

- Up to 3.4 GHz operation in N3P process

- Cache size up to 16 Kb

- 4 – 64-bit word width

- Configurable way associativity

- Custom logic-rules bitcell

- Speed / Static Power tradeoff option

Benefits

- Cache Types

- Data array

- Instruction array

- Virtual tag array

- Physical tag array, PTAG

- Cache Applications

- AI Processors

- Data Center

- High Performance Computing

- Network Compute Units

- Neural Processor

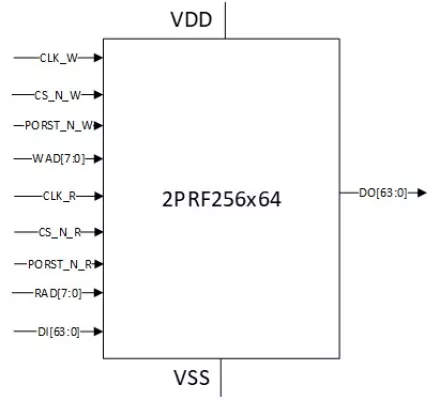

Block Diagram

Technical Specifications

Foundry, Node

TSMC, 3nm

Maturity

Silicon Proven

Availability

Now

Related IPs

- Viterbi Compiler, High-Speed Parallel Decoder

- Compact High-Speed 32-bit CPU Core with Level-2 Cache

- GDDR4 Controller - Validates high-speed memory controllers for efficiency and reliability

- LPDDR5 Controller - Validates memory controllers for high-speed, power-efficient performance

- DDR5 Controller - Ensures high-speed, efficient operation and compatibility of memory controllers

- FIR Compiler