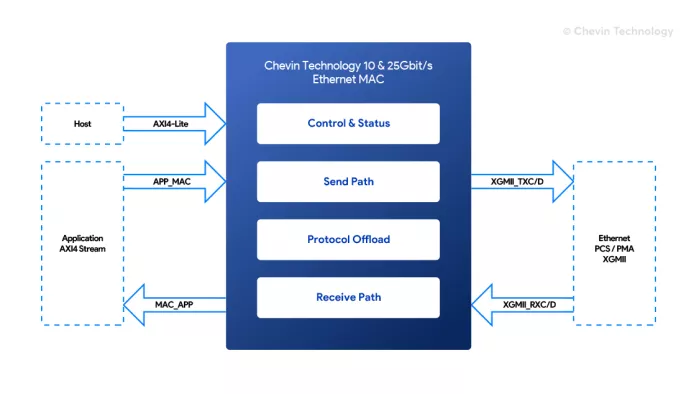

The Chevin Technology Ethernet MAC IP core can simplify the FPGA integration of Ultra low-latency 10/25/40/100G MAC Ethernet connectivity in Intel and AMD Xilinx FPGAs.

The MAC can be used directly with either an external or internal PCS, however, we recommend using Chevin Technology PCS for the lowest possible latency.

The application side can be driven by any logic that generates and decodes Ethernet frames. The MAC manages frame timing, CRC32 Checksum insertion and generation, and manages the lower layer fault handling and XGMII interface coding.

Flow control provides back pressure to peer node and is handled automatically by the MAC in both directions independently

A detailed statistics block provides a running count of frames sent and received with individual 64bit counters for different frame sizes, types and checksum errors.

10/25/40/100G Ethernet MAC

Overview

Key Features

- Designed to IEEE 802.3by specification

- Low latency, TX 11ns, RX 8ns (Modes: cut-through/store-and-forward)

- Integrated FCS(CRC32) checker and generator

- Small Footprint, Virtex UltraScale 2680 LUTs / 2 Block RAMs

- Pause packet generate/accept

- Deficit Idle Control / Programmable IFG, less gaps, more throughput

- Store-and-forward /Cut-Through FIFO modes for minimum workload/latency

- Statistics counters, TX and RX traffic stats collected in size bins, frame type, FCS errors

- Local/Remote fault handling at RS Sub-Layer

- MAC Filter/Promiscuous Mode

Benefits

- 10/25/40/100Gbit Ethernet Connectivity in Intel and AMD/Xilinx FPGAs

- A reference design is available for technology partner Bittware’s IA-840F and IA-420F boards, as well as Alpha Data’s ADM-PCIE-8V3, ADM-PCE-9V3 boards. The 10/25/40/100G MAC/PCS is also compatible with AMD/Xilinx’s VCU108 board and has been tested with the Mellanox MCX4121A-ACAT NIC.

- Easy to integrate, simple host interface to registers and statistics table.

Block Diagram

Applications

- Trade execution & monitoring

- Data Storage & Capture systems

- HPC / Big Data systems

- Signal processing systems

- Data Mining

Deliverables

- Encrypted RTL/VHDL source code for simulation

- Encrypted compiled netlist

- Datasheet & User Guide to assist integration

- Simulation Test bench

- Build scripts for Vivado

- Support for integration into FPGAs

Technical Specifications

Availability

Now