The Chevin Technology 25G LL MAC/PCS combines the 25G MAC and 25G PCS IP cores to obtain the lowest possible latency while simplifying the integration of 25Gbit/s Ethernet connectivity in Xilinx Virtex® UltraScale™ FPGAs.

Ultra-low latency is achieved on the PCS block by using only the PMA function in FPGA Multi-Gigabit transceivers and moving all PCS functions to code that is optimized for 25GBASE-R. This allows the data to take the shortest, and hence the lowest latency, path to and from the wire.

The MAC manages frame timing, CRC32 Checksum insertion and generation, and manages the lower layer fault handling and XXVGMII interface coding. Chevin Technology’s MAC/PCS is XXVGMII compatible with a 64bit interface at 390.625MHz. A detailed statistics block provides a running count of frames sent and received with individual 64bit counters for different frame sizes, types and checksum errors.

25G LL MAC /PCS Ethernet IP for FPGA

Overview

Key Features

- Ultra Low Latency 128 ns packet Round Trip Time (RTT) in Virtex® UltraScale™

- Integrated FCS CRC32 check/generate

- 7930 LUTs (MAC 2680 & PCS 5250LUTs)

- Flow Control option with Pause packets

- Deficit Idle Count / Programmable IFG– Minimize IFG

- Cut-through mode

- Store-and-forward

- Fault Management, BER monitoring

- Statistics counters for frames and bytes sent/received, size bins, FCS errors, broadcast

- Reference design on an AlphaData’s ADMPCIE 8V3 evaluation board and a simple “ping” command line with the UDP/ICMP/ARP options.

- Compatible with Xilinx’s VCU108 board

- Interoperable with the Mellanox MCX4121A-ACAT NIC.

Benefits

- Significantly increase the efficiency and rate of data transfer by providing lowest possible latency.

- Straightforward integration of 25Gbit/s Ethernet connectivity in Xilinx Virtex® UltraScale™ FPGAs.

- Cut-through mode operation minimizes latency

- Store-and-forward feature allows for minimum application load

- Competitively priced licenses available to suit the size and requirements of each project.

- Customers can evaluate the RTT for themselves using a bitfile on Chevin Technology’s eco-system partner Alpha Data’s ADM-PCIE-8V3 board

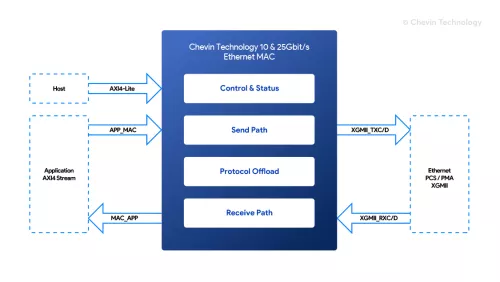

Block Diagram

Applications

- Trade execution & monitoring

- Data Storage & Capture systems

- HPC / Big Data systems

- Signal processing systems

- Data Mining

Deliverables

- Encrypted compiled netlist

- Datasheet & User Guide to assist integration

- Reference Design on Alpha-Data ADM-PCIE-8V3 board

- Simulation Test bench

- Build scripts for Vivado

- Support for integration into FPGA

Technical Specifications

Availability

Now