Cipher Accelerator IP

Welcome to the ultimate Cipher Accelerator IP hub! Explore our vast directory of Cipher Accelerator IP

All offers in

Cipher Accelerator IP

Filter

Compare

185

Cipher Accelerator IP

from 49 vendors

(1

-

10)

-

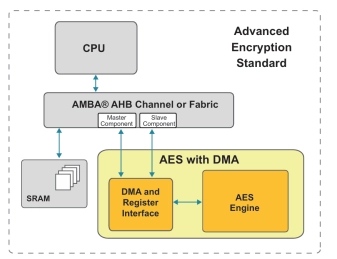

AHB AES with DMA

- The Advanced Encryption Standard (AES) IP Core is a complete hardware implementation encryption/decryption algorithm described in the U.S. Government Federal Information Processing Standards Publication 197 (FIPS 197).

- The AES IP Core implements the Rijndael algorithm which is a symmetric block cipher that can process 128-bit data blocks using 128, 192, or 256-bit cipher keys.

-

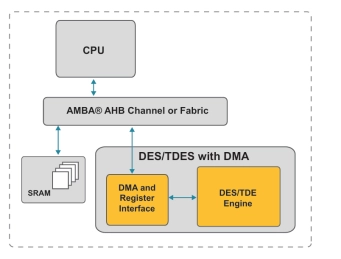

AHB DES and Triple DES with DMA

- The AHB DES/TDES Encryption/Decryption Engine is a configurable core that interfaces to an AHB microprocessor bus.

- The Controller encrypts or decrypts blocks of data based on the DES encryption standard.

- In order to accommodate a wide variety of system requirements, the Engine can be generated in two modes: LowLatency and LowGateCount. For a TDES system, three DES cores are instantiated.

-

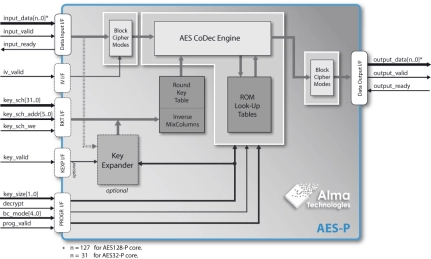

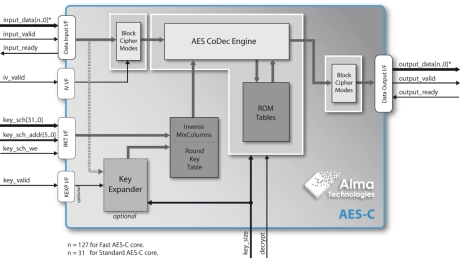

AES Encryption & Decryption IP Core − Programmable Block Cipher Modes

- The AES-P IP core implements the FIPS-197 Advanced Encryption Standard. It can be programmed to encrypt or decrypt 128-bit blocks of data, using 128-, 192-, or 256-bit cipher-key.

- The Block Cipher mode of operation is run-time programmable to ECB, CBC, CFB, OFB, or CTR. The AES-P core is available in two variations, the standard AES32-P and the fast AES128-P.

-

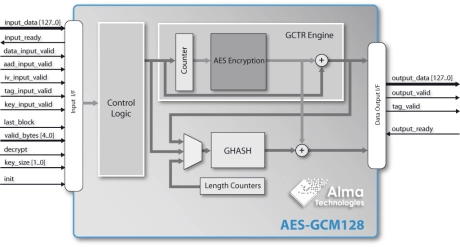

GCM-AES IP Core − Authenticated Encryption & Decryption

- Advanced Encryption Standard (AES - FIPS PUB 197) and NIST SP800-38D for GCM/GMAC compliance

- Run-time programmable encryption or decryption operation

- Run-time programmable cipher-key size: 128-, 192-, 256-bit

- Integrated Key Expansion module for automatic generation of the AES Round Key values

- 96-bit GCM Initialization Vector

-

AES Encryption & Decryption IP Core − Single Configurable Block Cipher Mode

- Compliant, High-Performance and Standalone Operation

- Trouble-Free Technology Map and Implementation

-

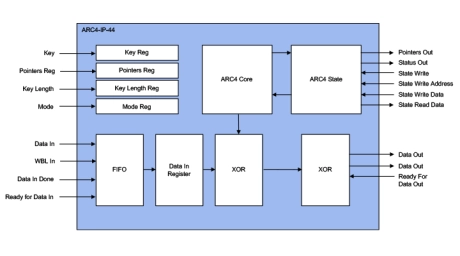

ARC4 Stream Cipher Accelerators

- The ARC4-IP-44 (EIP-44) is IP for accelerating the ARC4 stream cipher algorithm (used for legacy SSL & IPsec) up to 5 Gbps @ 600MHz.

- Designed for fast integration, low gate count and full transforms, the ARC4-IP-44 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high-speed crypto pipelines.

-

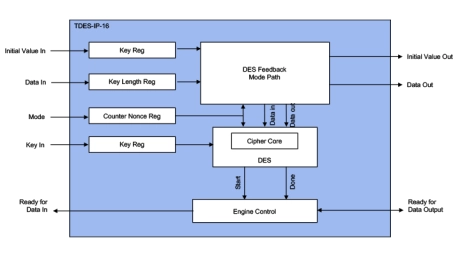

3DES ECB/CBC Accelerators

- The 3DES-IP-16 (EIP-16) is IP for accelerating the AES symmetric cipher algorithm (FIPS-46/81 – SP800-IP-20), supporting single Des and triple DES in ECB, CBC, CFB and OFB modes up to 4 Gbps @ 800MHz.

- Designed for fast integration, low gate count and full transforms, the 3DES-IP-16 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high speed crypto pipelines.

-

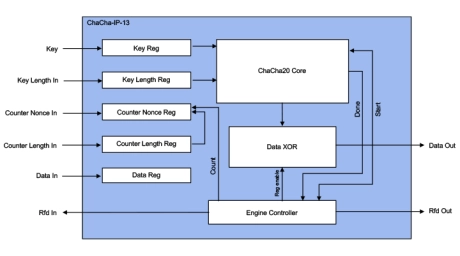

ChaCha20 Accelerators

- The ChaCha-IP-13 (EIP-13) is an IP solution for accelerating the ChaCha20 cipher algorithm (RFC7539), supporting the NIST CTR mode up to 12.8 Gbps @ 300MHz.

- Designed for fast integration, low gate count and full transforms, the ChaCha-IP-13 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high-speed crypto pipelines.

-

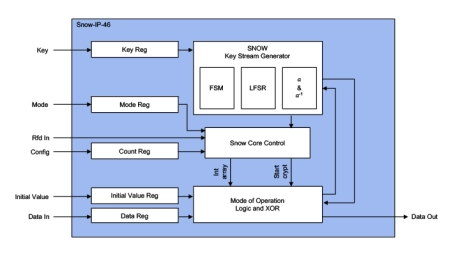

3GPP SNOW 3G Accelerators

- The SNOW-IP-46 (EIP-46) cipher accelerators implement the specification of the 3GPP Confidentiality and Integrity Algorithms as specified by 3GPP and ETSI.

- Designed for fast integration, low gate count and full transforms, the SNOW-IP-46 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high speed SoCs for base stations or other equipment requiring 3GPP support.

-

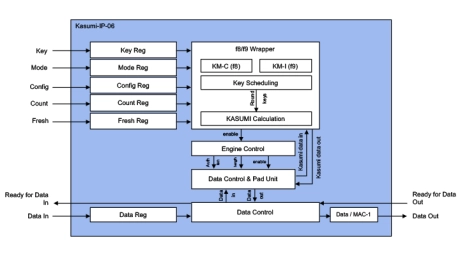

3GPP Kasumi Accelerators

- Wide bus interface (64-bit data, 128-bit keys) or 32-bit register interface.

- Includes key scheduling hardware.

- Modes Kasumi

- Algorithms f8 and f9.

- Fully synchronous design.

- Low Speed, High Speed versions.