DDR4 PHY IP

Welcome to the ultimate DDR4 PHY IP hub! Explore our vast directory of DDR4 PHY IP

All offers in

DDR4 PHY IP

Filter

Compare

66

DDR4 PHY IP

from 8 vendors

(1

-

10)

-

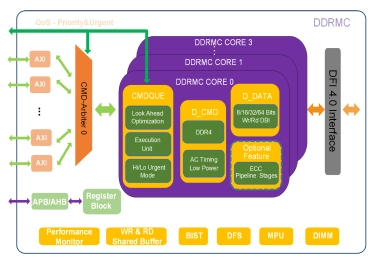

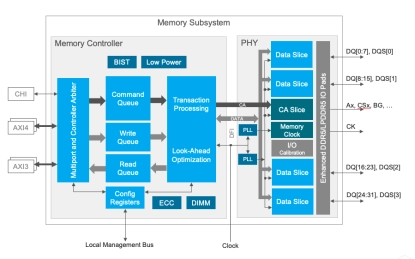

DDR4 IP solution

- Compatible with DDR4 up to 3200Mbps

- AXI compliant multi-ports, and data width, FIFO depth, command queue depth configurable

- DFI compliant interface between controller and PHY

- Support ECC (error correcting code)

-

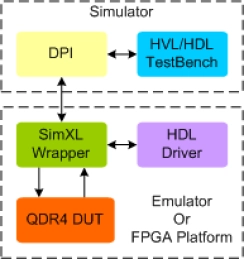

QDR4 Synthesizable Transactor

- Supports 100% of QDR4 protocol standard CY7C4142KV13

- Supports 144-Mbit density (8M × 18, 4M × 36)

- Supports eight-bank architecture enables one access per bank per cycle

- Supports two-word burst on all accesses

-

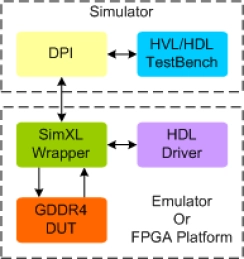

GDDR4 Synthesizable Transactor

- Supports 100% of GDDR4 protocol standard GDDR4Spec rev 04

- Supports all the GDDR4 commands as per the specs

- Supports all types of timing and protocol violation detection

- Supports all mode registers programming

-

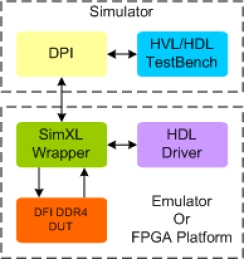

DDR4 DFI Synthesizable Transactor

- Compliant with DFI version 3.0 or higher Specifications.

- DFI-DDR4 Applies to :

- DDR4 protocol standard JESD79-4, JESD79-4A, JESD79-4A_r2,JESD79-4B, JESD79-4C and JESD79-4D (draft) Specification

- Supports all Interface Groups.

-

DDR PHY

- DDR5/4/3 training with write-leveling and data-eye training

- Optional clock gating available for low-power control

- Internal and external datapath loop-back modes

- I/O pads with impedance calibration logic and data retention capability

- Programmable per-bit (PVT compensated) deskew on read and write datapaths

- RX and TX equalization for heavily loaded systems

-

DDR4 multiPHY SP - SS 14LPP

- Support for JEDEC standard DDR4, DDR3, LPDDR2, and LPDDR3 SDRAMs

- Scalable architecture that supports data rates up to DDR4-2667

- Support for DIMMs

- Delivery of product as a hardened mixed-signal macrocell component allows precise control of timing critical delay and skew paths

-

DDR4 multiPHY - UMC 28HPC18

- Support for JEDEC standard DDR4, DDR3, LPDDR2, and LPDDR3 SDRAMs

- Scalable architecture that supports data rates up to DDR4-2667

- Support for DIMMs

- Delivery of product as a hardened mixed-signal macrocell component allows precise control of timing critical delay and skew paths

-

DDR4 multiPHY - TSMC 28HPC+18

- Support for JEDEC standard DDR4, DDR3, LPDDR2, and LPDDR3 SDRAMs

- Scalable architecture that supports data rates up to DDR4-2667

- Support for DIMMs

- Delivery of product as a hardened mixed-signal macrocell component allows precise control of timing critical delay and skew paths

-

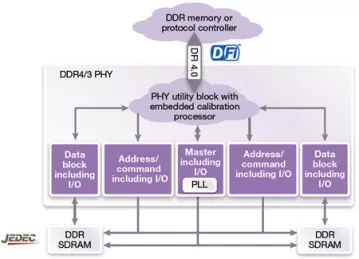

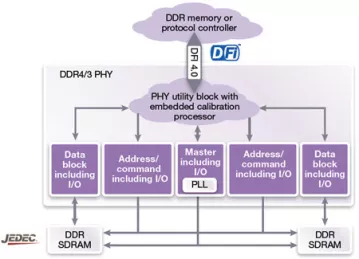

DDR4/3 PHY - TSMC 16FFC

- Supports JEDEC standard DDR4, DDR3, and DDR3L SDRAMs

- High-performance DDR PHY supporting data rates up to 3200 Mbps

- Compatible with JEDEC compliant DDR3/4 UDIMMs and RDIMMs as well as DDR4 LRDIMMs

- Supports up to 16 logical ranks for high capacity memory requirements

-

DDR4/3 PHY - TSMC 16FF+GL

- Supports JEDEC standard DDR4, DDR3, and DDR3L SDRAMs

- High-performance DDR PHY supporting data rates up to 3200 Mbps

- Compatible with JEDEC compliant DDR3/4 UDIMMs and RDIMMs as well as DDR4 LRDIMMs

- Supports up to 16 logical ranks for high capacity memory requirements