Multi-Protocol PHY IP for TSMC

Welcome to the ultimate Multi-Protocol PHY IP for TSMC hub! Explore our vast directory of Multi-Protocol PHY IP for TSMC

All offers in

Multi-Protocol PHY IP

for TSMC

Filter

Compare

88

Multi-Protocol PHY IP

for TSMC

from 4 vendors

(1

-

10)

-

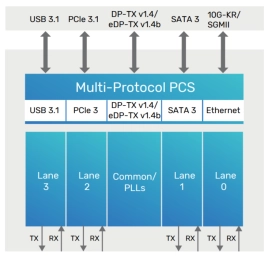

10Gbps Multi-Link and Multi-Protocol PCIe 3.1 PHY IP for TSMC

- Supports USB 3.1, PCIe 3.0/2.0/1.0, DP-TX v1.4/ eDP-TX v1.4b, SATA 3, 10G-KR and SGMII

- Supports PCIe L1 sub-states

- Supports SRIS and internal SSC generation

- Supports internal and external clock sources with clock active detection

-

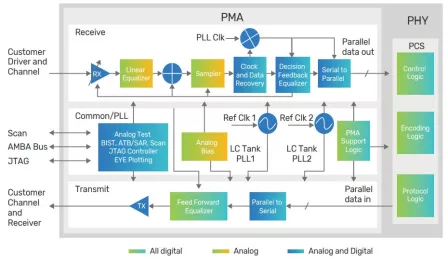

10Gbps Multi-Protocol PHY IP (+PCIe 3.1)

- Supports 10G-KR, PCIe 3.1/2.0/1.0, XAUI, Q/SGMII, and Gigabit Ethernet

- LC tank PLL with a wide range of reference clock frequencies and SSC

- High-performance decision feedback equalization and adaptive CTLE

- Serial and parallel loop-back functions

- Available in X1 through X10 lane configurations

-

25G PHY, TSMC N6 x2 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G PHY, TSMC 7FF x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G PHY, TSMC 7FF x2 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G PHY, TSMC 7FF x1 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G MR Ethernet PHY, TSMC 7FF x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G MR Ethernet PHY, TSMC 7FF x2 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G PHY, TSMC 16FFPGL x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G PHY, TSMC 16FFC x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features