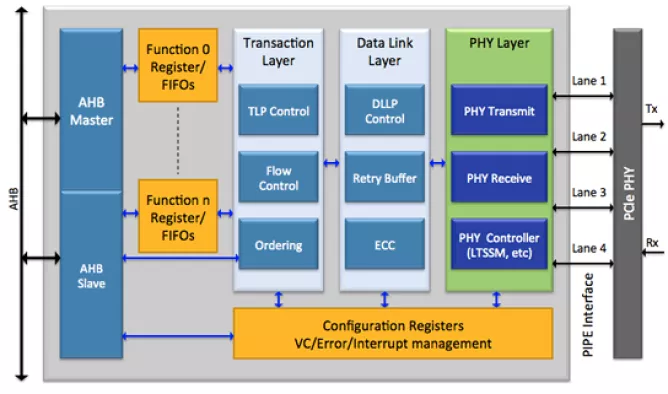

PCIe 2.0 End Point IP Core - PCIe with FIFO Interface

Overview

The Arasan PCI Express End Point is a high-speed, high-performance, and lowpowerIP core that is fully compliant to the PCI Express Specification 1.1 and 2.0. The IP core is designed for applications in computing, networking, storage, servers, wireless, and consumer electronics. The feature-rich IP core is highly configurable that allows a target design to be implemented with the least number of gates and highest performance.

Key Features

- PCI Express Specification Rev 1.1 and Rev2.0

- PIPE Specification Rev 1.87

- 8-bit/16-bit PIPE interface

- x1, x2, and x4 lanes

- ASPM and software controlled power management

- Legacy PCI, and MSI/MSI-X interrupts support

- AHB master/slave with FIFO interface

- Optional 8051 host interface

- Optional custom bus interface

Benefits

- Fully compliant core

- Premier direct support from Arasan IP core designers

- Easy-to-use industry standard test environment

- Unencrypted source code allows easy implementation

- Customer training available

- Reuse Methodology Manual guidelines (RMM) compliant verilog code ensured using Spyglass

Block Diagram

Deliverables

- RMM Compliant Synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

- Sample device drivers

Technical Specifications

Maturity

Compliant core

Availability

Now

Related IPs

- NVMe IP core -- Directly connect PCIe SSD without external memory

- PCIe 1.1 Controller supporting Root Port, Endpoint, Dual-mode Configurations, with Built-in DMA and Configurable AMBA AXI Interconnect

- NVMe over TCP IP core - End-to-End NVMe-oF TCP connectivity with no CPU!

- PSI5 IP Core Controller for Peripheral Sensor Interface 5 Communication

- PCIe 3.1 Controller with AXI

- PCIe 4.0 Controller with AXI