Highest performance IP for graphics, AI/ML

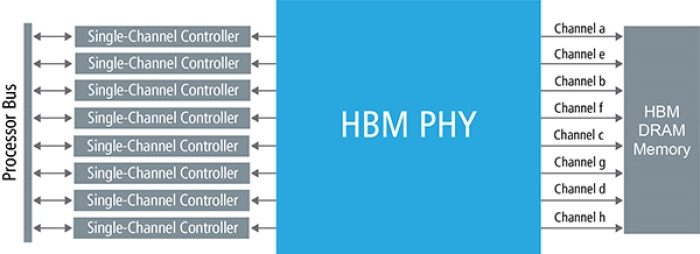

The High-Bandwidth Memory generation 2/2E PHY (HBM2E/2 PHY) is silicon-proven and is available in four process nodes: PHYs, achieving breakthrough performance, low energy per bit, and low area relative to the data bandwidth. It is engineered to quickly and easily integrate into SoCs and is verified as part of a complete memory subsystem solution. The HBM2E/2 PHY IP is an ideal solution for artificial intelligence (AI), high-performance computing (HPC), and image processing applications.