Clock Generator PLL IP for UMC

Welcome to the ultimate Clock Generator PLL IP for UMC hub! Explore our vast directory of Clock Generator PLL IP for UMC

All offers in

Clock Generator PLL IP

for UMC

Filter

Compare

100

Clock Generator PLL IP

for UMC

from 4 vendors

(1

-

10)

-

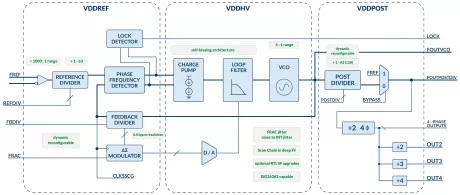

Fractional-N Frequency Synthesizer PLL

- Wide functional range allows all frequencies in a system to be synthesized with one PLL macro

- Input & output frequency ranges greater than 1000:1

-

High Performance Fractional-N RF Frequency Synthesizer PLLs for 5G, WiFi, etc

- Fractional-N digital PLL architecture, using an LC-tank oscillator

-

High Performance Fractional-N RF Frequency Synthesizer PLL in UMC 40LP

- Fractional-N digital PLL architecture, using an LC-tank oscillator

- Ultra-low jitter and ultra-low phase noise

-

Low Voltage, Low Power Fractional-N PLLs

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

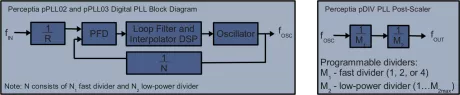

General Purpose Fractional-N PLLs

- Low power, suitable for logic clocking applications

- Extremely small die area, using a ring oscillator

- Twelve bits fractional resolution

-

Fractional-N PLLs for Performance Computing

- Low jitter, suitable for many clocking applications, including high speed digital, ADC, DAC, medium-speed PHY

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 4GHz

- Reference clock from 10MHz to 500MHz

-

Fractional-N PLL for Performance Computing in UMC40LP

- Low jitter, suitable for many clocking applications, including high speed digital, ADC, DAC, medium-speed PHY

- Extremely small die area (< 0.02 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 4GHz

- Reference clock from 10MHz to 500MHz

-

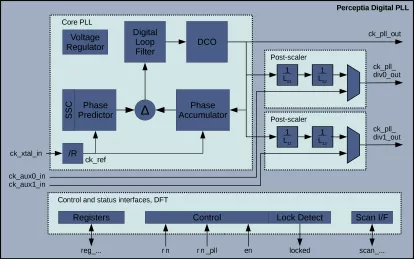

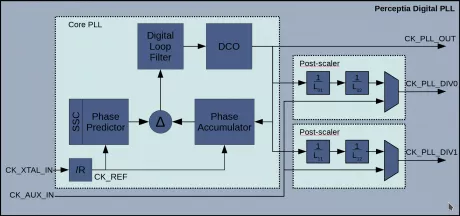

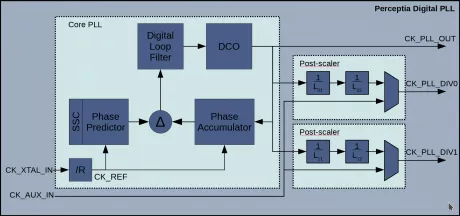

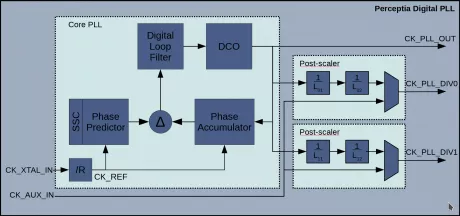

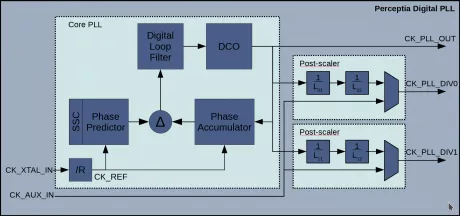

4-GHz Jitter-optimized low-power digital PLL

- - Jitter below 10-ps

- - Super small: 90 x 90 microns!

- - Very low power: 15-mW

- - Broad frequency range: 4-GHz

-

UMC L65LP 65nm Clock Generator PLL - 60MHz-300MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.

-

UMC L65LP 65nm Clock Generator PLL - 120MHz-600MHz

- Designed as a very flexible clock multiplier capable of multiplying an input clock from 1 to 4096 with very small period jitter while operating at the highest possible bandwidth.

- Delivers optimal jitter performance over all multiplication settings.

- Available with multi-phase outputs and, in some processes, with an I/O voltage regulator.

- Ideal for system clock generation, SerDes and video clock applications.