Memory Controller & PHY IP for TSMC

Welcome to the ultimate Memory Controller & PHY IP for TSMC hub! Explore our vast directory of Memory Controller & PHY IP for TSMC

All offers in

Memory Controller & PHY IP

for TSMC

Filter

Compare

41

Memory Controller & PHY IP

for TSMC

from 7 vendors

(1

-

10)

-

ONFI 4.1 NAND Flash Controller & PHY & IO Pads on 16nm

- Page Size – 2KB, 4KB, 8KB, 16KB

- Bank/chip select options

- Programmable timing

-

ONFI 4.1 NAND Flash Controller & PHY & IO Pads on 28nm

- Page Size – 2KB, 4KB, 8KB, 16KB

- Bank/chip select options

- Programmable timing

-

ONFI 4.1 NAND Flash Controller & PHY & IO Pads on 12nm

- Page Size – 2KB, 4KB, 8KB, 16KB

- Bank/chip select options

-

Secure Digital I/O offerings

- Secure Digital

- Physical Features

-

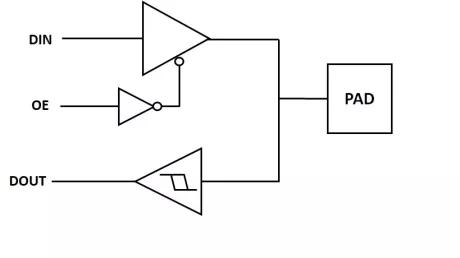

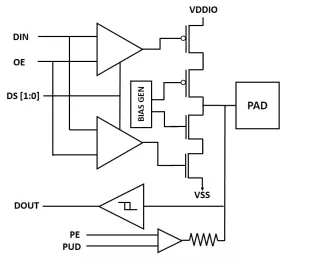

1.8V/3.3V Switchable GPIO With 5V I2C Open Drain & Analog in 16/12nm

- Multi-voltage 1.8V / 3.3V switchable operation

- 4 selectable drive strengths (25-235MHz @1.8V, 10pF)

- Full-speed output enable

- Independent power sequencing

-

TSMC N3P 1.8V IO Platform supporting cells

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

TSMC N3P SD/eMMC PHY North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

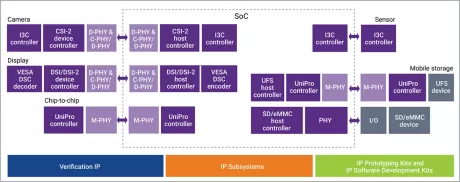

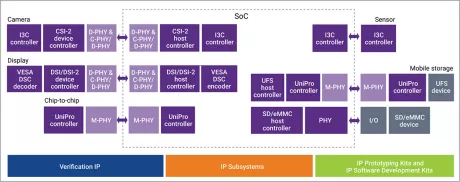

SD/eMMC - TSMC 7FF, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

SD/eMMC - TSMC 6FF, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

SD/eMMC - TSMC 28HPM, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution