Memory Interface IP for TSMC

Welcome to the ultimate Memory Interface IP for TSMC hub! Explore our vast directory of Memory Interface IP for TSMC

All offers in

Memory Interface IP

for TSMC

Filter

Compare

16

Memory Interface IP

for TSMC

from 3 vendors

(1

-

10)

Filter:

- 3nm

-

HBM3 PHY V2 - TSMC N3E

- Supports 2.5D-based JEDEC standard HBM3 DRAMs with data rates up to 9600 Mbps

- 16 independent 64-bit memory channels

- Pseudo-channel operation supported to enable up to 32 32-bit pseudo-channels with 1024-bit PHY

- Supports up to 4 trained frequencies with <5us switching time

-

HBM3 PHY V2 (Hard) - TSMC N3P

- Supports 2.5D-based JEDEC standard HBM3 DRAMs with data rates up to 9600 Mbps

- 16 independent 64-bit memory channels

- Pseudo-channel operation supported to enable up to 32 32-bit pseudo-channels with 1024-bit PHY

- Supports up to 4 trained frequencies with <5us switching time

-

HBM3 V2 Solution enabling access to HBM3 Controller and HBM3 PHY in TSMC N3E

- JEDEC HBM 3.0 DRAM

- DFI 5.0 compliant interface to HBM3 PHY

- Multiport Arm® AMBA® interface (4 AXI AXI™) with managed QoS or single-port host interface, per pseudo-channel

- Data rates up to 6.4 Gbps (DFI 1:1:2) (1.6GHz controller clock)

-

LPDDR5X/5/4X PHY - TSMC N3P

- Supports JEDEC standard LPDDR5X, LPDDR5 and LPDDR4X SDRAMs

- Support for data rates up to 8533 Mbps

- Designed for rapid integration with Synopsys LPDDR5X/5/4X controller for a complete DDR interface solution

- DFI 5.0 controller interface

-

LPDDR5X/5/4X PHY - TSMC N3E

- Supports JEDEC standard LPDDR5X, LPDDR5 and LPDDR4X SDRAMs

- Support for data rates up to 8533 Mbps

- Designed for rapid integration with Synopsys LPDDR5X/5/4X controller for a complete DDR interface solution

- DFI 5.0 controller interface

-

LPDDR5X/5/4X PHY - TSMC N3A for Automotive, ASIL B Random, AEC-Q100 Grade 2

- Supports JEDEC standard LPDDR5X, LPDDR5 and LPDDR4X SDRAMs

- Support for data rates up to 8533 Mbps

- Designed for rapid integration with Synopsys LPDDR5X/5/4X controller for a complete DDR interface solution

- DFI 5.0 controller interface

-

DDR5 PHY - TSMC N3P

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

DDR5 MRDIMM2 PHY - TSMC N3P

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

DDR5 PHY - TSMC N3E

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

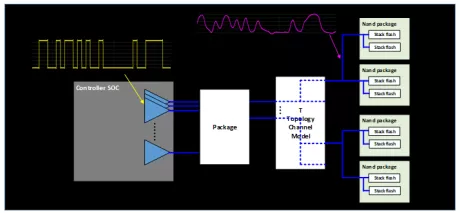

ONFI IO v6.0, 4.8GT/s, TSMC N3P, 1.2V, N/S orientation, H&V cell

- Supports ONFI 6.0(4.8Gbps), ONFI 5.1(3.6Gbps), ONFI 5.0(2.4Gbps), ONFI 4.1(1.2Gbps), ONFI 4.0(800Mbps) & ONFI 3.2(533Mbps)

- Power-sequence free

- Provides multi-driving-strength selection

- Provides CTT mode and LTT mode