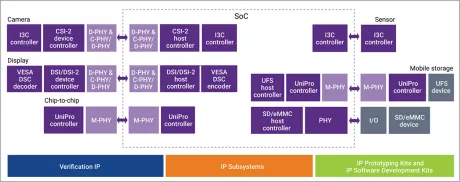

MIPI PHY IP for TSMC

Welcome to the ultimate MIPI PHY IP for TSMC hub! Explore our vast directory of MIPI PHY IP for TSMC

All offers in

MIPI PHY IP

for TSMC

Filter

Compare

39

MIPI PHY IP

for TSMC

from 5 vendors

(1

-

10)

Filter:

- 7nm

-

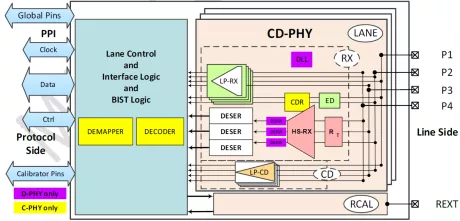

MIPI C-PHY/D-PHY Combo RX IP 4.5Gsps/4.5Gbps in TSMC N7

- Dual mode PHY Supports MIPI Alliance Specification D-PHYv2.5 & C-PHYv2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHYmode

-

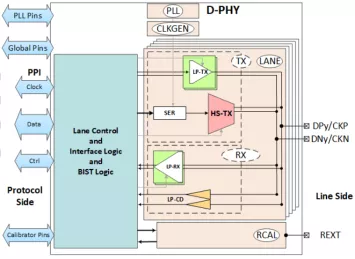

MIPI D-PHY IP 4.5Gbps in TSMC N7

- Supports MIPI Alliance Specification for D-PHY Version 2.5

- Consists of 1 Clock lane and 4 Data lanes

-

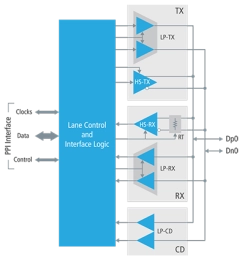

MIPI D-PHY

- Multiple Configurations Possible. TX-only (with integrated PLL), RX-only, and combined TX and RX configurations

- Complete Function for HS TX/RX, LP TX/RX, and LPCD with automatic termination control for high-speed and low-power modes

- Integrated BIST Capable of producing and checking PRBS, CRPAT, and CJTPAT

-

MIPI M-PHY Type 1 G5 2TX2RX - TSMC N7 1.8V, North/South Poly Orientation

- Compliant with MIPI M-PHY v5.0 specification

- Supports MIPI UniPro, JEDEC UFS protocols

- Supports High-Speed (HS) Gear1,

- Gear2, Gear3, Gear4 and Gear5 A/B modes

- Supports M-PHY Type-I

-

MIPI M-PHY G4 Type 1 2TX2RX - TSMC 7FF 1.8V, North/South Poly Orientation

- Compliant with MIPI M-PHY v5.0 specification

- Supports MIPI UniPro, JEDEC UFS protocols

- Supports High-Speed (HS) Gear1,

- Gear2, Gear3, Gear4 and Gear5 A/B modes

- Supports M-PHY Type-I

-

MIPI M-PHY G4 Type 1 2TX2RX - TSMC 7FF 1.8V, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 2

- Compliant with MIPI M-PHY v5.0 specification

- Supports MIPI UniPro, JEDEC UFS protocols

- Supports High-Speed (HS) Gear1,

- Gear2, Gear3, Gear4 and Gear5 A/B modes

- Supports M-PHY Type-I

-

MIPI D-PHY Tx 4 Lanes - TSMC7FF18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Tx 2 Lanes - TSMC7FF18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 4 Lanes - TSMC7FF18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 2 Lanes - TSMC7FF18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes