General Purpose PLL IP for SMIC

Welcome to the ultimate General Purpose PLL IP for SMIC hub! Explore our vast directory of General Purpose PLL IP for SMIC

All offers in

General Purpose PLL IP

for SMIC

Filter

Compare

54

General Purpose PLL IP

for SMIC

from 8 vendors

(1

-

10)

-

High Performance Fractional-N RF Frequency Synthesizer PLLs for 5G, WiFi, etc

- Fractional-N digital PLL architecture, using an LC-tank oscillator

-

Low Voltage, Low Power Fractional-N PLLs

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

General Purpose Fractional-N PLLs

- Low power, suitable for logic clocking applications

- Extremely small die area, using a ring oscillator

- Twelve bits fractional resolution

-

Fractional-N PLLs for Performance Computing

- Low jitter, suitable for many clocking applications, including high speed digital, ADC, DAC, medium-speed PHY

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 4GHz

- Reference clock from 10MHz to 500MHz

-

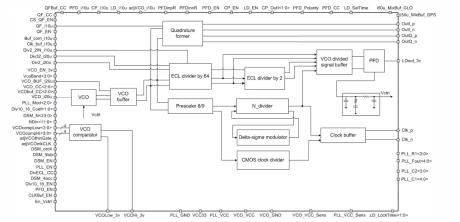

PLL system, 2.8 to 3.3 GHz

- SMIC CMOS 0.18 um technology

- Wide frequency range (2.8…3.3 GHz)

- Built-in switched capacitors sections for VCO frequency adjustment

- Low noise figure

-

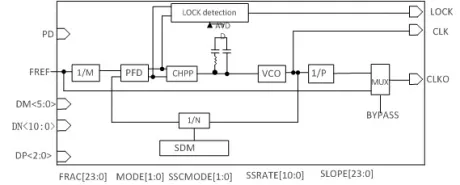

High Speed PLL

- Silicon proven in 22, 28, 40, 55, 65, 110, 130, 180nm from SMIC, HHgrace, GlobalFoundries and Samsung.

- Support integer mode, Fraction mode and Spread-Spectrum mode

- Input reference range:10MHz~100MHz

- Core Area:0.0678 mm^2

-

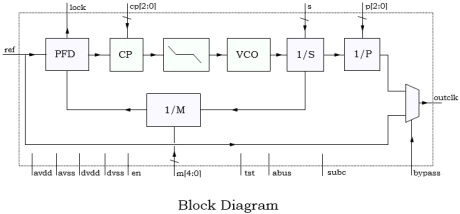

General Purpose PLL for TSMC 152nm

- Wide range M integer divider. (See ot3122 for M, N, and P dividers)

- 40MHz – 800MHz output frequency range.

- Comparable frequency range 8MHz – 32MHz.

- Optional prescaler.

- 19pS RMS cycle to cycle jitter at 800MHz.

- Lock-detect function.

- Bypass function.

- 20µS well defined fast startup behavior.

-

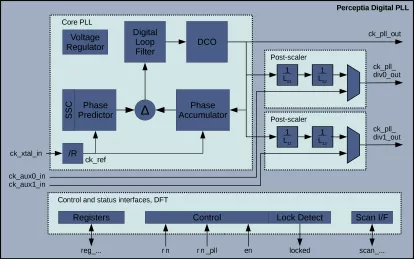

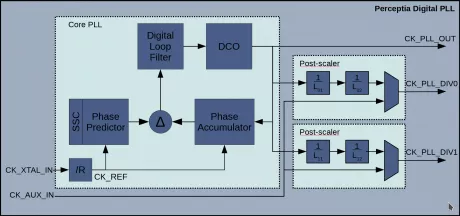

4-GHz Jitter-optimized low-power digital PLL

- - Jitter below 10-ps

- - Super small: 90 x 90 microns!

- - Very low power: 15-mW

- - Broad frequency range: 4-GHz

-

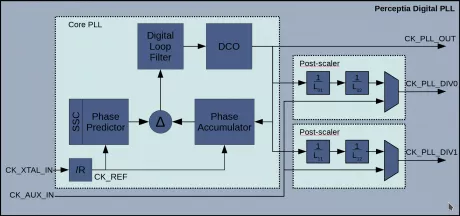

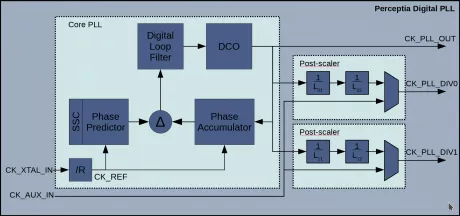

Minimum-area low-power clocking PLL (1st gen)

- - Super small: 80 x 80 microns!

- - Very low power: 12-mW

- - Broad frequency range: 2-GHz

- - Fast lock

-

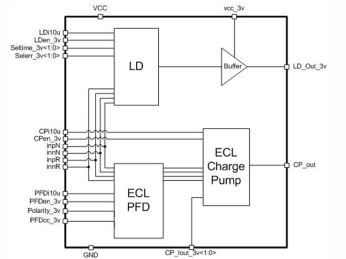

24.84 MHz phase-frequency detector with charge pump

- SMIC CMOS 0.18 um

- Charge pump current control (40 uA, 60 uA, 80 uA, 100 uA)

- Wide range of charge pump output voltage (0.3 V…1.56 V)

- PFD polarity selection