The JPEG-D core from Alma Technologies is a standalone and high-performance Baseline JPEG decoder for still image and video compression applications. Compliance with the Baseline Sequential DCT mode of the ISO/IEC 10918-1 JPEG standard makes the JPEG-D core ideal for interoperable systems and devices.

In addition to decoding standard Baseline JPEG streams, the core is also capable of decompressing the video payload of many (de facto) standard motion JPEG container formats.

The core is designed with simple, fully controllable and FIFO-like, streaming input and output interfaces. Being carefully designed, rigorously verified and silicon-proven, the JPEG-D is a reliable and easy-to-use and integrate IP.

Baseline JPEG Image & Video Decoder

Overview

Key Features

- Complete, Compliant and Standalone Operation

- ISO/IEC 10918-1 compliant 8-bit Baseline JPEG decoder

- Up to 64K x 64K image resolution

- Up to four stream programmable Quantization Tables

- Up to four stream programmable Huffman Tables (two DC, two AC)

- Stream programmable Restart Markers

- Single- and multi-scan support

- All three compressed data formats supported

- Interchange format

- Abbreviated format for compressed image data

- Abbreviated format for table-specification data

- Motion JPEG payload decoding

- CPU-less, complete and standalone operation

- Limitations with Respect to the ISO/IEC 10918-1 JPEG Standard

- Up to 4 image components

- Sampling factors 1, 2 and 4

- The DNL marker is not supported

- Decoding of corrupted JPEG streams is not supported

- Ease of Integration

- Automatic self-programming by JPEG markers parsing

- JPEG marker errors catching features

- Simple, microcontroller like, programming interface

- High-speed, flow controllable, streaming I/O data interfaces

- Simple and FIFO like

- Avalon-ST compliant (ready latency 0)

- AXI4-Stream compliant

- Trouble-Free Technology Map and Implementation

- Fully portable, self-contained RTL source code

- Strictly positive edge triggered design

- D-type only Flip-Flops

- Fully synchronous operation

- No special timing constraints required

- No false paths

- No multi-cycle paths

- Clear text VHDL or Verilog RTL source for ASIC designs, or pre-synthesized & verified Netlist for Altera, Lattice, Microsemi and Xilinx FPGA and SoC devices

- Release Notes, Design Specification and Integration Manual documents

- Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

- Self checking testbench environment, including sample BAM generated test cases

- Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts

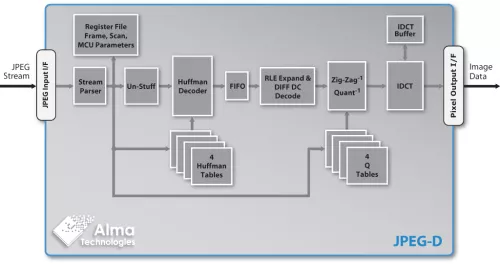

Block Diagram

Deliverables

Technical Specifications

Maturity

Silicon Proven

Availability

NOW

Related IPs

- 10/12-bit Extended and 8-bit Baseline JPEG Image & Video Decoder

- JPEG 2000 Encoder - Up to 16-bit per Component Lossy & Numerically Lossless Image & Video Compression

- Scalable UHD JPEG 2000 Encoder - 8 up to 16 bits per Component Lossy or Numerically Lossless Image & Video Compression

- Baseline JPEG Encoder with optional Constant Bitrate Motion JPEG Video Rate Control

- Baseline JPEG Codec with optional Constant Bitrate Motion JPEG Video Rate Control

- Lossless JPEG Encoder - Up to 16-bit per Component Numerically Lossless Image & Video Compression