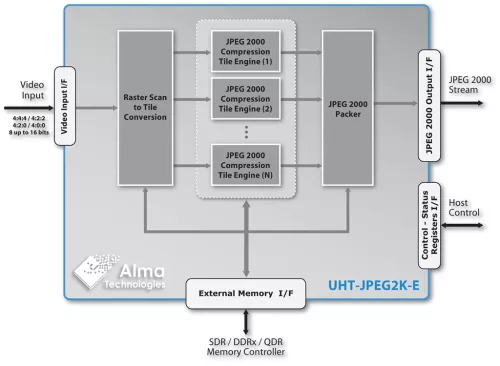

The UHT-JPEG2K-E core from Alma Technologies is a very high performance self-contained JPEG 2000 encoder IP core, designed to provide the extreme performance needed by modern image and video compression applications that have to cope with massive resolutions and pixel rates. The core implements Part 1 of ISO/IEC 15444-1 image compression standard and supports lossy and lossless encoding of 4:4:4, 4:2:2, 4:2:0 and 4:0:0 video streams, in 8 up to 16 bits sample depths.

Using multiple internal compression engines, the UHT-JPEG2K-E offers the needed performance through its scalable parallel architecture. Each input image or video frame is split internally into pieces and each piece is allocated to one of the multiple internal compression engines. The encoded output streams of the compression engines are combined in a single output stream. These operations are done in a way that is transparent to the system utilizing the IP, abstracting all the parallelization complexity from the rest SoC components. The number of internal compression engines is configurable before synthesis, adapting to the implementation technology speed, and non-critical resources are shared between the multiple compression engines.

Scalable UHD JPEG 2000 Encoder - 8 up to 16 bits per Component Lossy or Numerically Lossless Image & Video Compression

Overview

Key Features

- ISO/IEC 15444-1 Compliant and Standalone Operation

- Full compliance to the ISO/IEC 15444-1 JPEG 2000 specification

- 4:4:4, 4:2:2, 4:2:0 and 4:0:0 encoding

- 8 up to 16 bits sample depth encoding

- Up to 65535 x 65535 image resolution

- Up to 8192 x 8192 tile resolution

- Lossless or lossy compression

- Advanced rate control engine

- ISO/IEC 15444-1 compliant code stream (JPC) or file (JP2) JPEG 2000 output

- CPU-less, complete and standalone operation

- Advanced JPEG 2000 Implementation

- Ultra-high throughput in medium-end silicon

- Superior compression and video quality from ED to Ultra HD resolutions

- CBR image/video encoding mode

- Rate control option with programmable requested output compression ratios

- On-the-fly nominal output compression ratios changes are supported

- Medium requirements in external memory bandwidth

- Flexible external memory interface

- Independent of external memory type

- Tolerant to latencies

- Allows for shared memory access

- Can optionally operate on independent clock domain

- Easy Implementation and Verification

- Extensive documentation

- Bit Accurate Model (BAM) with optional Test Vector generation functionality

- Self-checking testbench environment

- Sample BAM scripts

- Synthesis scripts

- Simulation scripts

- Place & Route scripts for FPGAs

- Trouble-Free Technology Map and Implementation

- Fully portable HDL source code

- No internal tri-states

- Strictly positive edge triggered design

- D-type only Flip-Flops

- Fully synchronous operation

- Safe CDC transfers

- No need for special timing constraints

- No false or multi-cycle paths within the same clock domain

- No CDC transfers that need to be constrained

- No specially constrained timing paths

Block Diagram

Technical Specifications

Availability

NOW

Related IPs

- JPEG 2000 Encoder - Up to 16-bit per Component Lossy & Numerically Lossless Image & Video Compression

- Lossless JPEG Encoder - Up to 16-bit per Component Numerically Lossless Image & Video Compression

- CCSDS 122.0-B-1 Encoder - Lossless and Lossy Image Data Compression with up to 16 bits Pixel Dynamic Range

- Scalable UHD JPEG Encoder – Ultra-High Throughput, 8/10/12-bit per component and CBR video encoding

- Scalable UHD JPEG Decoder – Ultra-High Throughput, 8/10/12-bit per component

- Video Encoder IP – 4k60 Scalable up to 8K120