25Gbit/s Ethernet PCS

Overview

The Chevin Technology 25GPCS provides Ultra low-latency 25Gbit/s Ethernet connectivity in Xilinx Virtex® UltraScale™ FPGAs. Ultra-low latency is achieved by using only the PMA function in FPGA Multi-Gigabit transceivers, and moving all PCS functions to code that is optimized for 25GBASE-R. This allows the data to take the shortest and lowest latency path, to and from the wire. The 25GPCS /PMA core can be used directly with Multi-Gigabit Transceivers (SerDes & CDR logic) in Xilinx Virtex® UltraScale FPGAs for the lowest possible latency.

Key Features

- Designed to IEEE 802.3by

- Low Latency PCS/PMA (RTT) 99 ns

- 5250 LUTs

- Integrated 64b66b encoder/decoder

- Integrated Scrambler/Descrambler

- Gearbox for rate conversion

- Fault management, BER monitoring

- Clock Rate adaptation, TX/ RX

- Detailed traffic analysis statistics collection

- XXVGMII interface, 64bit @ 390.625MHz

- Connect directly using SFP28

- Use 4-channel for QSFP28 interfaces

Benefits

- Ultra Low Latency to reduce round trip time

- High performance for exceptionally fast, reliable data delivery

- Easy to integrate with other Chevin Technology IP cores

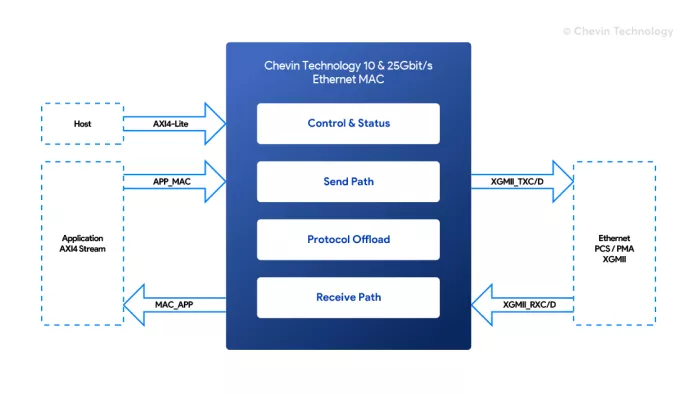

Block Diagram

Applications

- HPC / Big Data systems

- Trade execution & monitoring

- Data Storage & Capture systems

- Signal processing systems

- Data Mining

Deliverables

- Encrypted RTL/VHDL source code

- Encrypted compiled netlist

- Datasheet & User Guide to assist integration

- Reference Design for Alpha Data’s ADM-8V3 board

- Simulation Test bench

- Build scripts for Vivado

- Support for integration into FPGA

Technical Specifications

Availability

Now