Clock Generator PLL IP

Welcome to the ultimate Clock Generator PLL IP hub! Explore our vast directory of Clock Generator PLL IP

All offers in

Clock Generator PLL IP

Filter

Compare

417

Clock Generator PLL IP

from 17 vendors

(1

-

10)

-

General-purpose & Specialized Ring PLLs + RTL-based Solutions

- Wide functional range allows all frequencies in a system to be synthesized with one PLL macro

- Input & output frequency ranges greater than 1000:1

-

High Performance Fractional-N RF Frequency Synthesizer PLLs for 5G, WiFi, etc

- Fractional-N digital PLL architecture, using an LC-tank oscillator

-

High Performance Fractional-N RF Frequency Synthesizer PLL in UMC 40LP

- Fractional-N digital PLL architecture, using an LC-tank oscillator

- Ultra-low jitter and ultra-low phase noise

-

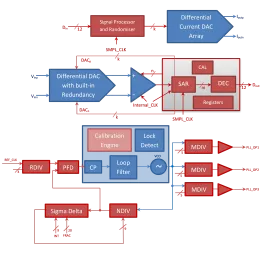

40nm 1.1V AFE comprising 12-bit IQ ADC, 12-bit IQ DAC and Clock-PLL

- Rail-to-Rail IQ ADC Input Capability

- 65dB IQ ADC SNR

- Programmable Full-Scale IQ DAC Output Current

- 65dB IQ DAC SNR

-

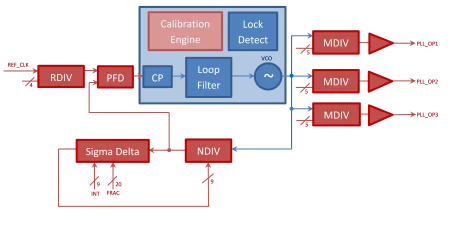

40nm 1.1V 16MHz-2GHz Fractional-N Clock-PLL

- 16MHz-to-2GHz PLL Output Coverage

- Scalable Power Consumption

- Three independent programmable PLL outputs

- Internal Calibration Engine and Convergence Algorithm

-

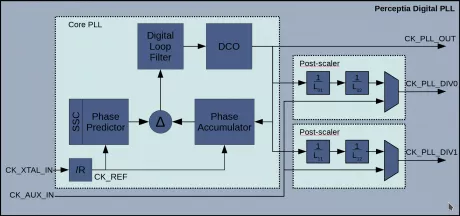

Low Voltage, Low Power Fractional-N PLLs

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

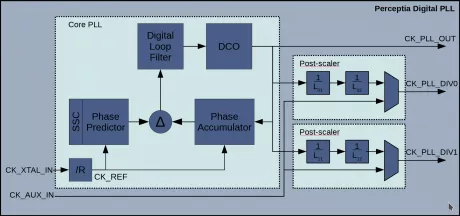

Fractional-N PLL for Performance Computing in GlobalFoundries 12LPP/14LPP

- Low jitter, suitable for many clocking applications, including high speed digital, ADC, DAC, medium-speed PHY

- Extremely small die area (< 0.004 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 4GHz

- Reference clock from 10MHz to 500MHz

-

Fractional-N PLL for Performance Computing in GlobalFoundries 22FDX

- Low jitter, suitable for many clocking applications, including high speed digital, ADC, DAC, medium-speed PHY

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 4GHz

- Reference clock from 10MHz to 500MHz

-

General Purpose Fractional-N PLLs

- Low power, suitable for logic clocking applications

- Extremely small die area, using a ring oscillator

- Twelve bits fractional resolution

-

Low Voltage, Low Power Fractional-N PLL

- GlobalFoundries GF22FDX

- Small size (< 0.005 sq mm)

- Low Power (< 0.7mW)