Graphics Controller IP

Filter

Compare

77

IP

from

17

vendors

(1

-

10)

-

Advanced 2D Graphics Controller

- Fully synchronous, synthesizable and technology independent RTL code

- Capable of drawing shapes such as pixels, lines and rectangles

-

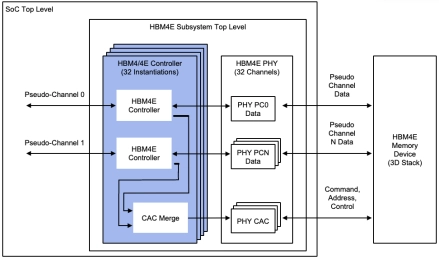

HBM4E Controller IP

- Supports HBM4/4E memory devices

- Supports all standard HBM4 channel densities (up to 32 Gb)

- Supports up to 16 Gbps/pin

- Refresh Management (RFM) support

-

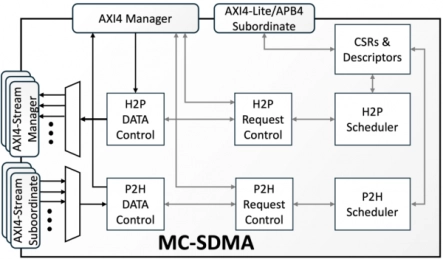

Multi-Channel Streaming DMA Controller

- The MC-SDMA IP core implements a highly configurable, bandwidth-efficient, and easy-to-use Direct Memory Access (DMA) controller that transfers data between the host system’s memory and multiple peripherals equipped with streaming interfaces.

- The core interfaces with the host memory via a manager AMBA® AXI4 (memory-mapped) port and provides access to its configuration and status registers (CSRs) via a subordinate AXI4-Lite or APB4 interface.

-

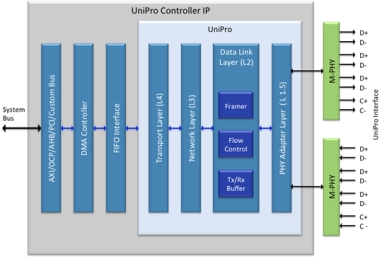

UniPro℠ Controller IP Core

- The UniPro Controller IP core is fully compliant with the UniPro specification version 1.6 and supports the physical adapter layer of the M-PHY® specification.

- MIPI UniPro is a high-performance, chip-to-chip, serial interconnect bus for mobile applications. Designed to support up to 5Gbps per data lane, it is scalable from one to four bidirectional lanes.

-

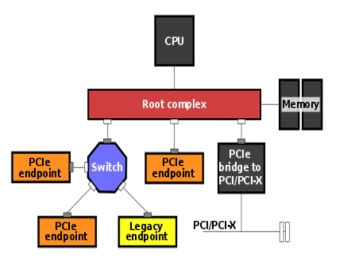

PCIe - PCI Express Controller

- The PCIe 3.0 (Peripheral Component Interconnect Express 3.0) is a computer hardware interface standard that is used to connect various components to a computer's motherboard.

- It is the third generation of the PCIe standard and offers increased bandwidth, improved performance, and reduced power consumption compared to its predecessor, PCIe 2.0 Overall, PCIe 3.0 provides faster and more efficient communication between the various components in a computer, including graphics cards, network adapters, and storage devices, resulting in better overall performance.

-

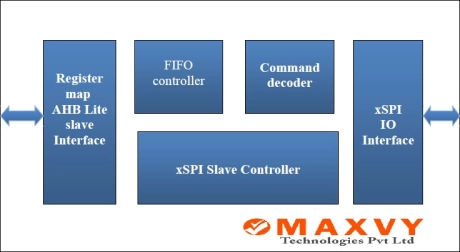

Expanded Serial Peripheral Interface (xSPI) Slave Controller

- The JESD251 Expanded Serial Peripheral Interface Slave controller is provides high data throughput, low signal count, and limited backward compatibility with legacy Serial Peripheral Interface(SPI) devices

- It is used to connect xSPI Master devices in computing, automotive, Internet of Things, Embedded system and mobile system processor to non-volatile memories, graphics peripherals, networking peripherals,FPGAs, sensors devices

-

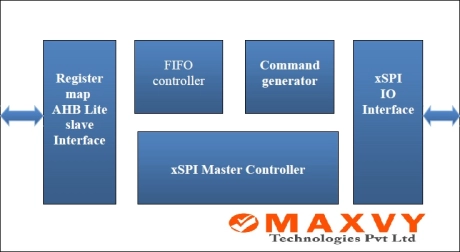

Expanded Serial Peripheral Interface (xSPI)Master Controller

- The Expanded Serial Peripheral Interface (JESD251) Master controller is low signal count, high data bandwidth, primarily for use in computing, automotive, Internet of Things, Embedded system and mobile system processor to connect multiple source of Serial Peripheral Interface (xSPI) slave devices like non-volatile memories, graphics peripherals, networking peripherals,FPGAs, sensors devices

-

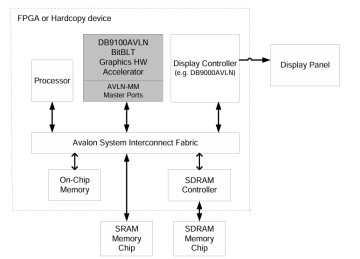

BitBLT Graphics Hardware Accelerator (Avalon Bus)

- The DB9100AVLN BitBLT Graphics Hardware Accelerator Verilog IP Core renders a graphics frame by generating new bitmaps from commands to combining existing bitmaps on and off-screen using one of 256 Raster Operations.

- A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT).

-

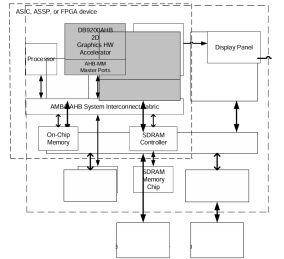

2D Graphics Hardware Accelerator (AHB Bus)

- Generates bitmaps from graphics instructions as well as combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT) which lay the foundation for power hardware graphics primitive operations

- Generates characters from compressed bitmaps using its FONT Bitmap Color Expansion Unit

- Performs Alpha Blend operations of bitmaps with its Alpha Blend unit

- Draws lines, polygons, circles using its hardware efficient & pixel accurate Bresenham Algorithm Line Drawing Unit

-

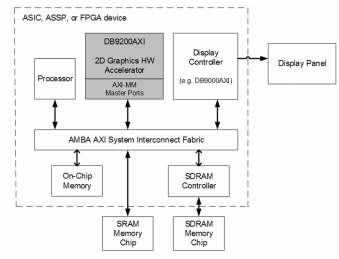

2D Graphics Hardware Accelerator (AXI Bus)

- Generates bitmaps from graphics instructions as well as combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT) which lay the foundation for power hardware graphics primitive operations

- Generates characters from compressed bitmaps using its FONT Bitmap Color Expansion Unit

- Performs Alpha Blend operations of bitmaps with its Alpha Blend unit

- Draws lines, polygons, circles using its hardware efficient & pixel accurate Bresenham Algorithm Line Drawing Unit