LPDDR3 Controller IP

Welcome to the ultimate LPDDR3 Controller IP hub! Explore our vast directory of LPDDR3 Controller IP

All offers in

LPDDR3 Controller IP

Filter

Compare

16

LPDDR3 Controller IP

from 6 vendors

(1

-

10)

-

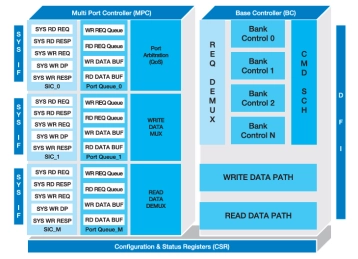

Universal Multi-port Memory Controller for RLDRAM2/3, DDR4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- The UMMC Controller is a highly flexible and configurable design. It is targeted for high bandwidth access and low power consumption such as next generation mobile, DDR/LPDDR networking and consumer applications.

- The controller architecture is carefully tailored to achieve reliable high-frequency operation with dynamic power management and rapid system debug capabilities.

-

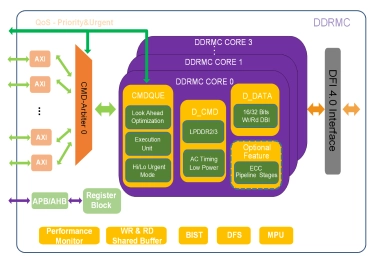

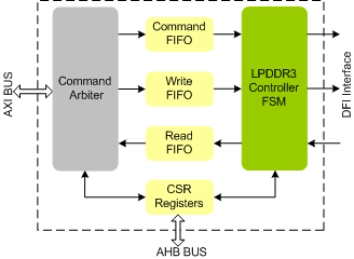

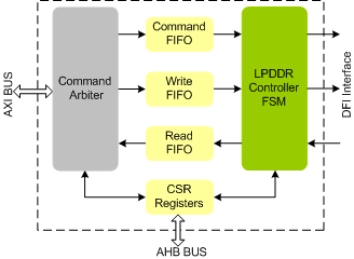

LPDDR3 IP solution

- Compatible with LPDDR3 up to 2133Mbps

- AXI compliant multi-ports, and data width, FIFO depth, command queue depth configurable

- DFI compliant interface between controller and PHY

- Support ECC (error correcting code)

-

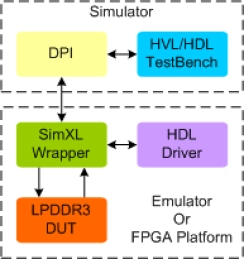

LPDDR3 Synthesizable Transactor

- Supports 100% of LPDDR3 protocol standard JESD209-3, JESD209-3B and JESD209-3C

- Supports all the LPDDR3 commands as per the specs

- Supports up to 32GB device density

- Supports the following devices:

-

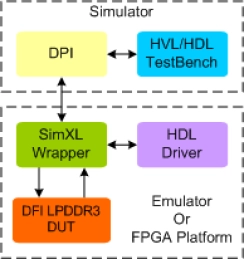

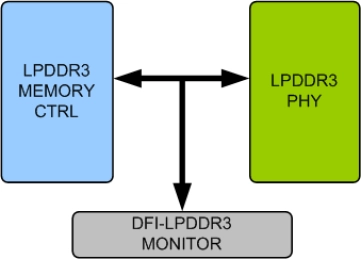

LPDDR3 DFI Synthesizable Transactor

- Compliant with DFI version 3.1 or higher Specifications.

- Supports LPDDR3 devices compliant with JEDEC LPDDR3 SDRAM Standard JESD209-3.pdf, JESD209-3B.pdf and JESD209-3C.pdf

- Supports for Read data-eye training.

- Supports for Read gate training.

-

LPDDR3 DFI Verification IP

- Compliant with DFI version 3.1 or higher Specifications.

- Supports LPDDR3 devices compliant with JEDEC LPDDR3 SDRAM Standard JESD209-3.pdf, JESD209-3B.pdf and JESD209-3C.pdf

- Supports for Read data-eye training

- Supports for Read gate training

-

LPDDR3 Controller IIP

- Supports 100% of LPDDR3 protocol standard JESD209-3, JESD209-3B and JESD209-3C.

- Compliant with DFI version 3.1 or higher Specification.

- Supports all the LPDDR3 commands as per the specs.

- Supports up to 16 AXI ports with data width upto 512 bits.

-

LPDDR Controller IIP

- Supports LPDDR protocol standard and JESD209A-1 and JESD209B Specification

- Compliant with DFI version 2.0 or higher Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transcations for AXI write and read channels

-

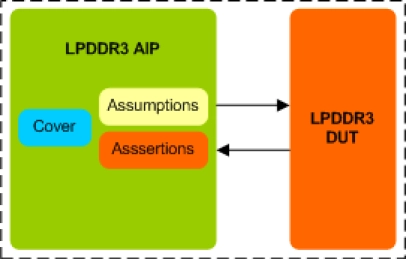

LPDDR3 Assertion IP

- Specification Compliance

- Supports all signal level checks including X detection

- Support for check-points include power on, Initialization and power off rules,

- Support for state based rules, Active Command rules,

-

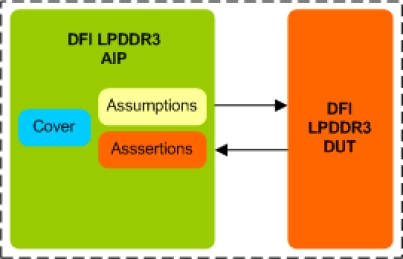

LPDDR3 DFI Assertion IP

- Specification Compliance

- Compliant with DFI version 3.1 or higher Specifications.

- Supports LPDDR3 devices compliant with JEDEC LPDDR3 SDRAM Standard JESD209-3.pdf, JESD209-3B.pdf and JESD209-3C.pdf.

- Supports for Read data-eye training.

-

LPDDR Controller

- Memory controller interface complies with DFI standard up to 5.0

- Application-optimized configurations for fast time to delivery and lower risk

- Sideband and in-line SEC/DED ECC

- Supports advanced RAS features including error scrubbing, parity, etc.

- Compliant to LPDDR5/4X/4/3 protocol memories

- Priority per command on Arm®AMBA® 4 AXI, AMBA 3 AXI