DDR2 IP

Welcome to the ultimate DDR2 IP hub! Explore our vast directory of DDR2 IP

All offers in

DDR2 IP

Filter

Compare

32

DDR2 IP

from 11 vendors

(1

-

10)

-

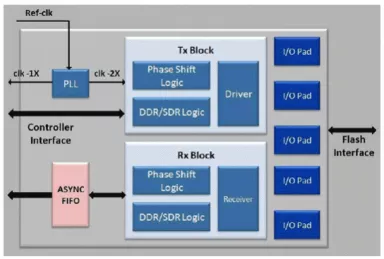

ONFI 3.2 NV-DDR2 PHY in GDSII

- Compliant to ONFI revision 3.2 standard

- Supports NV-DDR2 mode of operation supporting up to 266MHz or 566MT/s

- Supports NV-DDR mode of operation supporting up to 100MHz

- Supports legacy Asynchronous devices operating from 10MHz to 50MHz

-

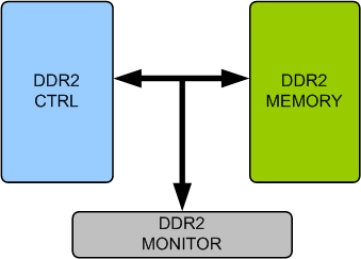

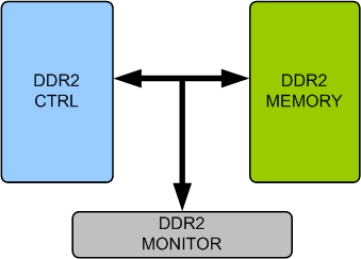

DDR2 Monitor Verification IP

- Supports DDR2 memory devices from all leading vendors

- Quickly validates the implementation of the DDR2 standard

- Constantly monitors DDR2 behavior during simulation

- Checks for following

-

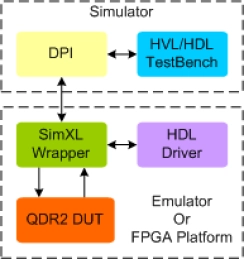

QDR2 Synthesizable Transactor

- Supports 100% of QDR2 protocol standard CY7C1314CV18

- Supports separate independent read and write data ports with concurrent read and write operation

- Supports full data coherency, providing most current data

- Supports synchronous pipeline read with self-timed late write

-

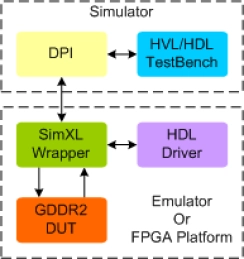

GDDR2 Synthesizable Transactor

- Supports 100% of GDDR2 protocol standard

- Supports all the GDDR2 commands as per the specs

- Supports all types of timing and protocol violation detection

- Supports all mode registers programming

-

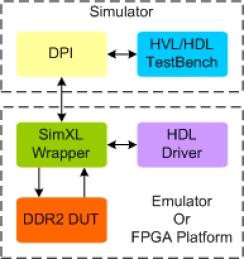

DDR2 Synthesizable Transactor

- Supports 100% of DDR2 protocol standard JESD79-2F

- Supports all the DDR2 commands as per the specs

- Supports double data rate interface

- Supports up to 4 GB device density

-

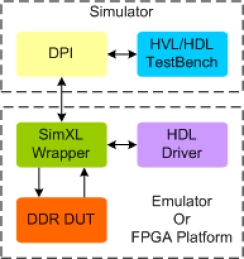

DDR Synthesizable Transactor

- Supports 100% of DDR protocol standard JESD79F

- Supports all the DDR commands as per the specs

- Supports all device speeds as per specification

- Supports programmable CAS latency

-

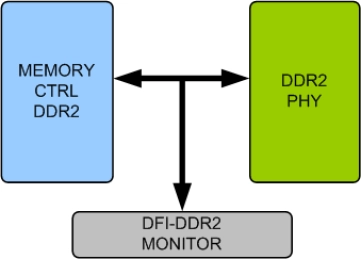

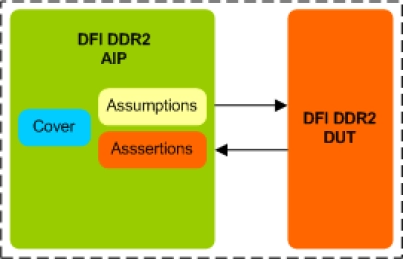

DDR2 DFI Verification IP

- Compliant with DFI version 2.0 or higher Specification.

- DFI-DDR2 Applies to :

- DDR2 protocol standard JESD79-2F Specification

- Supports all Interface Groups.

-

DDR2 Memory Model

- Supports DDR2 memory devices from all leading vendors.

- Supports 100% of DDR2 protocol standard JESD79-2F.

- Supports all the DDR2 commands as per the specs.

- Supports double data rate interface.

-

DDR2 DFI Assertion IP

- Specification Compliance

- Compliant with DFI version 2.0 or higher Specification.

- DFI-DDR2 Applies to :

- DDR2 protocol standard JESD79-2F Specification

-

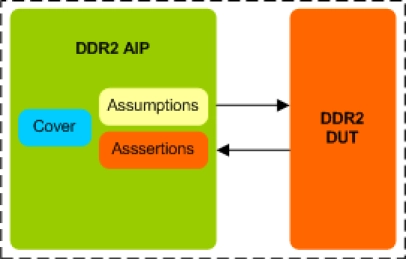

DDR2 Assertion IP

- Specification Compliance

- Compliant with DDR2 specifications.

- Supports all DDR2 data widths and address widths.

- Supports all DDR2 bank address widths.