DDR IP for Samsung

Welcome to the ultimate DDR IP for Samsung hub! Explore our vast directory of DDR IP for Samsung

All offers in

DDR IP

for Samsung

Filter

Compare

28

DDR IP

for Samsung

from 4 vendors

(1

-

10)

-

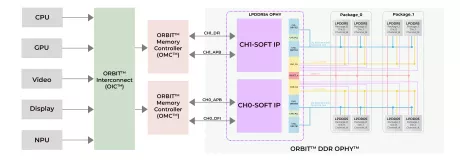

LPDDR5X/5/4X/4 combo PHY at Samsung SF5A

- Compliant for JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

- x16 and x32 channel support

-

DDR4 multiPHY SP - SS 14LPP

- Support for JEDEC standard DDR4, DDR3, LPDDR2, and LPDDR3 SDRAMs

- Scalable architecture that supports data rates up to DDR4-2667

- Support for DIMMs

- Delivery of product as a hardened mixed-signal macrocell component allows precise control of timing critical delay and skew paths

-

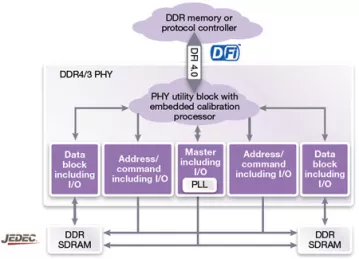

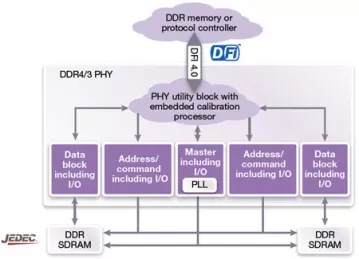

DDR4/3 PHY - SS 8LPP

- Supports JEDEC standard DDR4, DDR3, and DDR3L SDRAMs

- High-performance DDR PHY supporting data rates up to 3200 Mbps

- Compatible with JEDEC compliant DDR3/4 UDIMMs and RDIMMs as well as DDR4 LRDIMMs

- Supports up to 16 logical ranks for high capacity memory requirements

-

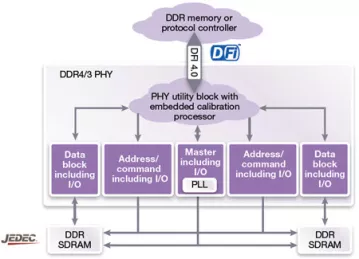

DDR4/3 PHY - SS 14LPP

- Supports JEDEC standard DDR4, DDR3, and DDR3L SDRAMs

- High-performance DDR PHY supporting data rates up to 3200 Mbps

- Compatible with JEDEC compliant DDR3/4 UDIMMs and RDIMMs as well as DDR4 LRDIMMs

- Supports up to 16 logical ranks for high capacity memory requirements

-

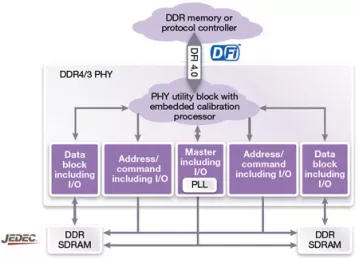

DDR4/3 PHY - SS 11LPP

- Supports JEDEC standard DDR4, DDR3, and DDR3L SDRAMs

- High-performance DDR PHY supporting data rates up to 3200 Mbps

- Compatible with JEDEC compliant DDR3/4 UDIMMs and RDIMMs as well as DDR4 LRDIMMs

- Supports up to 16 logical ranks for high capacity memory requirements

-

DDR4/3 PHY - SS 10LPP

- Supports JEDEC standard DDR4, DDR3, and DDR3L SDRAMs

- High-performance DDR PHY supporting data rates up to 3200 Mbps

- Compatible with JEDEC compliant DDR3/4 UDIMMs and RDIMMs as well as DDR4 LRDIMMs

- Supports up to 16 logical ranks for high capacity memory requirements

-

DDR5/4 PHY V2C CU - SS SF4X

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

DDR5 PHY - SS SF4X

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

DDR5/4 PHY V2 - SS 8LPU

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

DDR5/4 PHY - SS 7LPP

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time