VESA DSC V1.2 Decoder

Overview

Arasan’s VESA DSC v1.2 decoder IP core compresses high-definition streams in real time at resolutions ranging from 480 to 8K. The core supports 8, 10, 12, 14 or 16 bits per pixel in RGB or YCbCr format (4:4:4 or 4:2:2). The DSC Encoder core is industry-standard in its integration of host setup and control, data input, and visual output. Arasan’s VESA DSC decoder IP is seamlessly integrated with Arasan’s DSI Rx IP. Arasan’s expertise is backed by our unique silicon-proven design discipline and product development process that ensures fast silicon success with our analog and digital IP.

Key Features

- • Capable of decoding up to 4K video at 30fps in FPGA and 8K video at 30fps in ASIC applications

- • Low gate count and low latency implementation

- • Three clock domains

- • Stream and APB clocks operate the applicable interfaces

- • Independent decoder clock runs the core functions

- • Fully compliant with the VESA DSC 1.2 standard

- • Uses synchronous design techniques and a technology abstraction layer for internal SRAM buffers

- • Allows for migration from FPGA or FPGA prototype to ASIC with no functional changes to the core

- • Completely pipelined; can be stalled as necessary to properly manage input and output rates

Benefits

- • Fully compliant to VESA standards

- • Small footprint

- • Code validated with HAL and 0-in-CDC

- • Functionality ensured with comprehensive verification

- • Product quality proven with silicon

- • Premier direct support from Arasan IP core designers

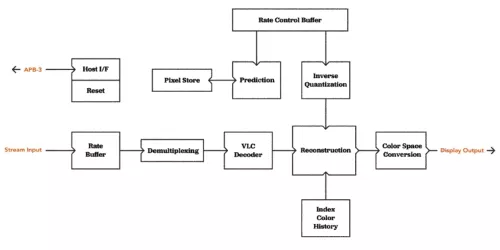

Block Diagram

Deliverables

- • Verilog HDL of the IP Core

- • Synthesis scripts

- • Verification environment

- • User guides for design and verification

Technical Specifications

Foundry, Node

TSMC & GF