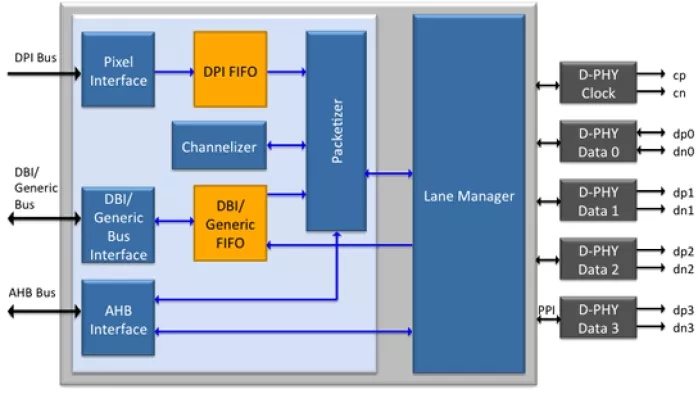

The Arasan DSI-2 Device Controller IP is designed to provide MIPI DSI-2 1.0 compliant high speed serial connectivity for mobile host processors using 1 to 4 D-PHYs depending on bandwidth needs. Serial connectivity to the display module’s DSI device is implemented using 1 to 4 D-PHY’s (also available from Arasan), depending on display bandwidth needs. This IP connects to the D-PHY’s through the PPI interface.

On the application processor side, Arasan’s DSI Host Controller provides the choice of DPI or DBI Interface to a graphics controller. A DBI interface provides downstream support of Types 1 to 3 display modules, and the DPI Interface is needed for Types 2 to 4 displays.

Initial configuration of this IP can be done through programmed IO over the AHB bus, however, other bus interfaces can be provided upon request.

MIPI DSI-2 Transmit Controller v1.0

Overview

Key Features

- Compliant with the following MIPI specifications

- Display Serial Interface (DSI) version 1.02

- Display Pixel Interface (DPI-2) version 2.00

- Display Bus Interface (DBI) version 2.00

- Display Command Set (DCS) version 1.02

- D-PHY version 1.2

- DSI Host-side (display module) interface supports

- Connectivity to D-PHY through PPI Interface

- 1 to 4 data lane support

- Hi-Speed (HS) transmit from 80 Mbps to 1.5Gbps per lane

- Low Power (LP) receive/transmit from/to device at 10 Mbps

- Continuous and stoppable clocks on clock lane

- Bus turnaround with contention and fault recovery

- Switching to and from Low Power (LP) and Ultra-low Power (ULPS) modes

- EOT enable/disable mechanisms

- Multiple packets per transmission with interleaved data stream

- Programmable error injection in Verification IP and error detection in design IP

- Supports flexibility in setting polarity for DPI Interface signals

- Application Processor Connectivity and video/command processing

- DPI or DBI, depending on panel or display unit architecture

- Generic command support

- Generic parallel interface for sending and receiving vendor-specific information to and from the display driver logic in the display module

- Support for all generic read/writes over DBI/Generic interface

- Video mode support

- Supports wide range of display resolution and pixel formats

- Supported display resolutions: QQVGA, QCIF, QVGA, CIF,VGA,WVGA, XGA, 1080p, QXGA, QSXGA

- Burst mode and non-burst transfers over DPI interface

- DBI support

- Supports 8/9/16-bit data transfer in DBI Type B interface

- Supports all DCS commands

- AHB Interface for register configuration and monitoring using programmed IO

Benefits

- Fully compliant to MIPI standard

- Small footprint

- Code validated with Spyglass

- Functionality ensured with comprehensive verification

- Product quality proven with silicon

- Premier direct support from Arasan IP core designers.

Block Diagram

Deliverables

- Verilog HDL of the IP Core

- Synthesis scripts

- Verification environment

- User guides for design and verification

Technical Specifications

Maturity

Silicon Proven

Availability

Now