The APB GPIO is a configurable module allowing the use of up to 32 scalable I/O lines. If more than 32 I/Os are required, more than one GPIO module may be instantiated.

Each line can be configured independently resulting in a very useful I/O application. The GPIO module supports a wide variety of options concerning synchronization logic and interrupt signal, which can be triggered by either a low level, high level, positive or negative edge. The GPIO is also fully compatible with the industry-standard APB bus interface.

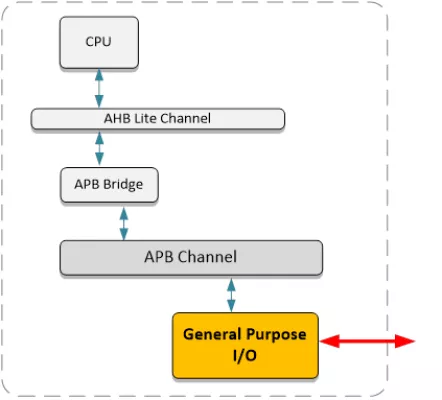

The GPIO module is a standard APB Slave peripheral, and has a standard APB Slave Port. The APB Slave Port is typically connected to one of the various APB Mirrored-Slave Ports of an APB Channel module. The several GPIO registers are accessed through its APB interface.

APB General Purpose IO

Overview

Key Features

- Scalable up to 32 I/Os

- Each I/O is independent

- Interrupt control for each I/O

- Selectable level sensitive or edge triggered interrupt system

- Supports asynchronous inputs

- AMBA APB bus interface

Block Diagram

Deliverables

- Verilog Source

- Complete Test Environment

- APB Bus Functional Model

- C-Sample Code

Technical Specifications

Maturity

Silicon Proven

Availability

Now

Related IPs

- 3.3V general purpose I/O for 28nm CMOS

- 1.8V general purpose I/O for 4nm FinFET

- APB4 General Purpose Input/Output Module

- General Purpose Input / Output Controller (GPIO)

- PLL general purpose / DDR memory, 50-500Mhz, 4 phases (0/90/180/270)

- General Purpose 10-bit DAC - 10 bits, 2MSPS, buffered output option - LFoundry 0.15µm LF150 CMOS