A radiation-hardened GlobalFoundries 12nm LP/LP+ Flip-Chip IO library with both 1.8V and 3.3V GPIO, fail-safe GPI, analog cell, and associated ESD. Also features an LDO optimized for use with 3.3V GPIO.

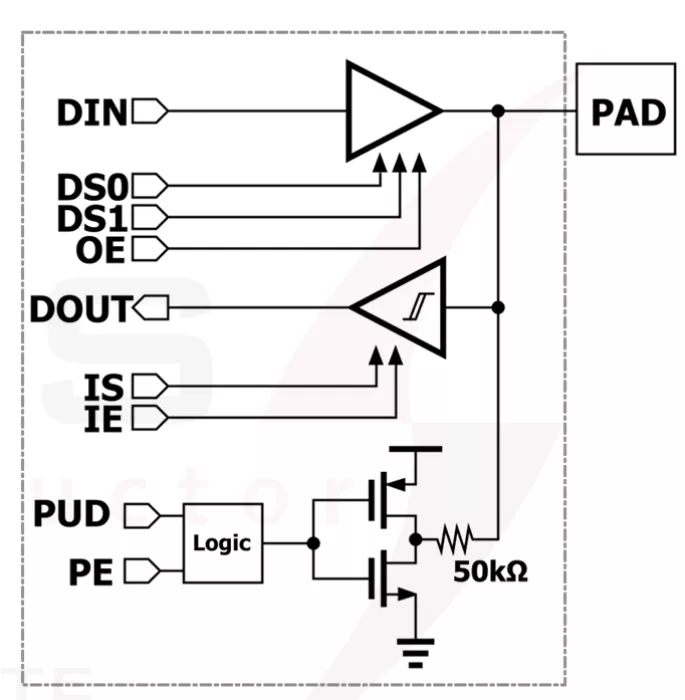

This radiation-hardened, by design, library features both a 1.8 and 3.3V GPIO with multiple drive strengths of 2mA, 4mA, 8mA, and 16mA, along with a full-speed output enable function. The library includes an LDO to generate a 1.8V refer ence which has been optimized for use with the 3.3V GPIO. The library incorporates radiation-hardened ESD cells, which are silicon-proven. A fail-safe GPI allows user to interface with bus-type protocols like I2C. All cells support independent power sequencing and integrate power-on-control circuitry for a clean low-leakage power-up. A selectable Schmitt trigger receiver adds input flexibility, while a 50K ohm pull-up or pull-down resistor is available for termination configurations. The library is enriched with feed-through, filler, transition, and domain-break cells to allow for flexible pad ring construction while maintaining ESD robustness. ESD targets are 2KV HBM / 500V CDM with 2KV IEC 61000-4-2 system stress capability.