Arithmetic & Logic Unit IP

Welcome to the ultimate Arithmetic & Logic Unit IP hub! Explore our vast directory of Arithmetic & Logic Unit IP

All offers in

Arithmetic & Logic Unit IP

Filter

Compare

9

Arithmetic & Logic Unit IP

from 5 vendors

(1

-

9)

-

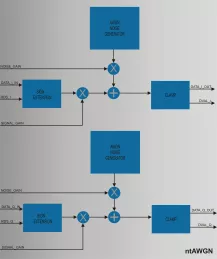

Additive White Gaussian Noise Generator

- High precision AWGN Channel emulator.

- Programmable Pseudo Random Generator(LFSR).

- Programmable number of output bits.

-

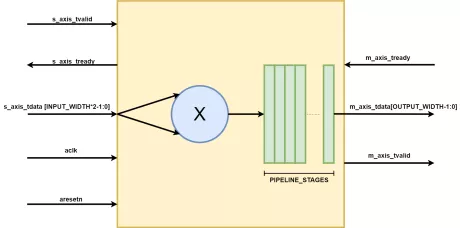

Parameterizable pipelined multiplier

- Synthesizeable, technology-independent IP Core for FPGA/ASIC and SoC

- Coded with SystemVerilog

- Wrapped with AXI Stream interface

- 16-bit Fixed-Point Representation/Operation

- Suitable for DSP or Machine Learning Applications

-

Very Small Form-Factor Division Core

- Optimized design allows customers to target cost efficient FPGAs.

- Can be tailored to customer needs

- Fully synchronous design using only one clock

- Area/Power efficient architecture

-

Floating Point Megafunctions

- Floating-point computation performance is typically a balanced combination of the frequency at which the operators run and the pipeline latency of the operator hardware. This product yields a measure of GFlop performance metric. When designing for maximum GFlop performance in an FPGA, the total number of operators that can be placed in an FPGA is vital. As such, you can parameterize the Altera floating-point megafunctions in many different ways to fine-tune GFlop performance (or, similarly, for other key metrics such as power and area) to meet the application-specific requirements. The configurable features include: